# Design and Analysis of a Two stage Class AB Operational Trans-conductance Amplifier in 180 –nm Technology

Shahrbanoo Ghorbanzadeh<sup>1</sup>, Hadi Dehbovid<sup>2\*</sup>, Alireza Ghorbani<sup>1</sup>, Seyed Mehdi AbediPahnekolaei<sup>1</sup>

**Abstract**–This paper presents design concept of Operational Transconductance Amplifier (OTA). Using active loads in the first stage and improved recycling structure, the effective transconductance of the first stage is increased. Nonlinear current mirror boosts the current of the second stage; Therefore, Slew Rate (SR) is increased. The class-AB technique is achieved without enhancing power dissipation and without unity-gain bandwidth (UGBW) or noise deterioration. The efficiency of the proposed OTA is evaluated by several simulations in a 0.18 $\mu$ m CMOS process with the 1.8 V supply voltage. This technique is very helpful for high amplification, stability, and low power applications. From the simulation results, the two stage amplifier gives better performance compared to other topologies, especially in terms of gain, output swing, slew rate and unity-gain bandwidth. The circuit is able to achieve 95 dB gain, a 3V output swing, a 172 (V/ $\mu$ s) slew rate and a unity-gain bandwidth of 344 MHZ with a power supply voltage of 1.8 V.

**Keywords**: Operational Trans-Conductance Amplifier; OTA specifications; post layout simulation; Figures of Merits.

## 1. Introduction

Operational trans-conductance amplifier (OTA) is an important building block for analog circuits and systems. The OTAs are utilized in various applications such as switched-capacitor circuits, data converters and continuous time filters and low dropout voltage regulators [1-3]. Designing the OTAs may be critical for emerging portable electronic devices. In applications such as very highresolution delta-sigma modulators and low dropout voltage regulators, the OTA should drive large capacitive loads and meanwhile keep high enough the DC gain, unity- gain bandwidth, and slew rates, while operating under low voltage supply and low static power [4-6]. Achieving these specifications are not viable using class-A OTAs. This is mainly due to the fact that the increasing of slew rate and unity- gain bandwidth would lead to increase power dissipation, considerably. Bulk-driven methods based low

power OTAs have been proposed in [7-9]. The main disadvantage existent in this technique is that bulk-source trans-conductance is smaller than the gate-source trans-conductance and may not be enough in some applications.

Class- AB OTAs can be considered as a better solution for the realization of the above specifications. In multi-stage amplifiers, cascading of every gain stage can be useful to enhancement the total DC-gain. But, a medium frequency pole is generated by each stage which can deteriorate the phase margin [10]. A Positive feedback technique can be employed to boost the tail current of the input stage. The circuit can become unstable due to variations of process and environmental parameters [11]. Combined method using the bulk-driven and positive-feedback techniques is proposed in [3]. An OTA with bulk-driven input stage is proposed in which bulk trans-conductance is improved using the positive-feedback. But, some specifications such as input referred noise may not be desirable.

To dominate the deficiency of the class-A OTAs, the class-AB OTA can be helpful [12]. Several techniques for class-AB OTAs have been reported in the literature [12-21]. Class-AB OTAs suggested in [12] have high values for current efficiency (CE) factors. This improvement in CE is obtained by increasing the maximum value of the signal current both in the input and output branches. However,

$Nour Branch, Islamic\ Azad\ University,\ Nour,\ Iran.\ Email:$

hadi.dehbovid@yahoo.com..

Received: 2022.09.09; Accepted: 2022.11.08

<sup>1</sup> Department of Electrical Engineering, Sari Branch, Islamic Azad university, Sari, Iran. Email: Sh\_ghorbanzadeh@yahoo.com.....

$<sup>{\</sup>bf 2^{*}\ Corresponding Author:} Department\ of\ Electrical iEngineering,$

these methods suffer from low open-loop gain. A technique to achieve class AB operation is suggested with the cost of enhancement the power consumption and silicon area of the circuit [13]. Some class-AB techniques have been applied to the recycling folded cascode (RFC) OTA [14-15]. But, the OTAs need additional local common-mode feedback loops at the active load of the differential pair which should be implemented by passive or active matched resistors. In addition, improvements in some specifications, such as DCgain, are not significant. In another method [16], an adaptive biasing circuit (ABC) for classic fully differential circuits has been introduced using dynamically control the bias current of the amplifier. However, circuit area and power dissipation have been increased due to auxiliary blocks. In [17], a class-AB OTA based on single-stage topology with non-linear current amplifiers has been introduced. But, some target specifications such as DC-gain and SR have not been improved significantly. In [18], a class AB RFC OTA has been suggested using current starving and transition between ohmic and saturation region for dynamic current boosting. Although power consumption is low, DC-gain and SR are not adequate. Some low-current OTAs have been suggested in [19-21]. But, technology or temperature sensitivity in the proposed class-AB OTAs is the main drawback of these techniques.

In this paper, a new two-stage class-AB OTA is proposed. The trans-conductance enhancement of the first stage is achieved via the simultaneous use of the active loads and the RFC technique. Therefore, the DC-gain of the OTA is increased. Enhancement of the SR is obtained using the nonlinear current mirror (NLCM). The rest of the paper is organized as follows. In Section 2, the proposed OTA is introduced. The performance evaluations of the OTA and comparison results are given in Section 3. Finally, Section 4 concludes the paper.

# 2. Proposed OTA

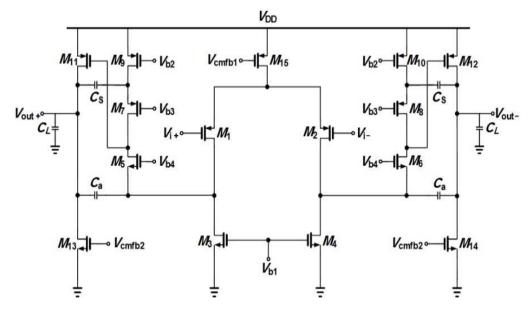

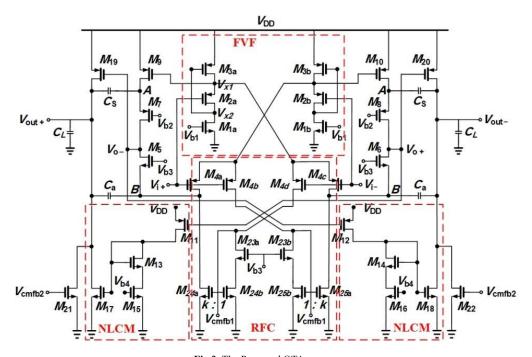

The conventional two- stage OTA using hybrid-cascade compensation technique is shown in Figure 1 [22]. The Figure 2 demonstrates the circuit configuration of the proposed class-AB OTA. In this Figure, *Vo* and *Vout* indicate the output voltages of the first and second stages, respectively.

In Figure 2, a flipped voltage follower (FVF) including the transistors  $(M_{1a}, M_{1b}, M_{2a}, M_{2b}, M_{3a}, M_{3b})$  are utilized as an ABC. When a large differential input signal is applied to the OTA, the FVF can deliver more current than the quiescent current. Therefore, it operates in class-AB and this characteristic can be useful for low-power applications

[23-24]. The RFC block is also shown in Figure 2. Input signals are applied to the split transistor sets  $(M_{4a}, M_{4b})$  and  $(M_{4c}, M_{4d})$  which have the same aspect ratio.  $M_{24a}: M_{24b}$  and  $M_{25a}: M_{25b}$  with a ratio of k:1 are used as current mirrors. To improve matching,  $M_{23a}: M_{23b}$  are employed to maintain the drain potentials of  $M_{24a}: M_{24b}$  and  $M_{25a}: M_{25b}$  equal [20]. The Source of  $(M_{4a}, M_{4b})$  is connected to the drain of  $M_{3b}$  and to the gate of  $M_{10}$ . similarly, Source of  $(M_{4c}, M_{4d})$  is connected to the drain of  $M_{3a}$  and to the gate of  $M_9$ . Therefore, the class-AB operation can be obtained for the active load transistors  $M_9$  and  $M_{10}$  related to the common-gate transistors  $M_5$  and  $M_6$

In this circuit, the gate of M9 and  $M_{10}$  are connected to the input stage using the FVF. Therefore, the transconductance of the input is increased from  $g_{m1,2}$  to  $g_{meff 1} = g_{m4a}(1+k) + g_{m9,10}$  which enhance the DC- gain. Increasing the input stage trans-conductance can also reduce the total input-referred noise voltage as follows:

$$\overline{V_{ni,pro}^2} = \frac{8kT\gamma}{g_{meff1}^2} \left[ g_{m4b} (1+k^2) + (g_{m25a} + g_{m25b} k^2) + g_{m9} \right] (1)$$

The nonlinear current mirrors (NLCMs) have been used for the output active loads including transistor sets  $(M_{11}, M_{13}, M_{15}, M_{17})$  and  $(M_{12}, M_{14}, M_{16}, M_{18})$ . To active the nonlinear current mirrors (NLCMs), the gates of  $M_{11}$  and  $M_{12}$  are connected to the first stage outputs  $V_{o+}$  and,  $V_{o-}$  respectively. The transistors  $M_{15}$  and  $M_{16}$  are biased near the triode region so that their drain-source voltages are a bit higher than  $V_{\rm DS,sat}$  [12].It should be noted that the transistors  $M_{16}$  and  $M_{18}$  should be biased in the vicinity of the triode region and saturation region, respectively. As a result, the current through  $M_{18}$  is given by

$$I_{18} = \frac{\beta_{18}}{2} \left( \frac{\sqrt{2I_{12}}}{\beta_{14}} + \frac{2I_{12}}{\lambda_{16}\beta_{16} (V_{b4} - V_{th})^2} - \frac{1}{\lambda_{16}} \right)^2$$

(2)

Where  $\beta_{18} = \mu_n C_{ox} (W/L)_{18}$ ,  $\lambda$  is the modulation parameter and  $V_{th}$  represents the threshold voltage. The current through is given by

$$I_{12} = \frac{\beta_{12}}{2} (V_{GS12} - V_{th})^2 = \frac{\beta_{12}}{2} (V_{DD} - V_{o-} - V_{th})^2$$

(3)

The voltage  $V_{a-}$  of this node can be obtained as below:

Fig 1. The conventional OTA [22].

Fig 2. The Proposed OTA.

$$V_{o-} = g_{meff1} \frac{V_{id}}{2} R_{out1} + V_{CMO1}$$

(4)

where  $V_{CMO1}$  is the first stage common-mode output voltage. Substituting (4) in (3), the drain current of  $M_{12}$  is obtained:

$$I_{12} = \frac{\beta_{12}}{2} (V_{DD} - g_{meff} \frac{V_{id}}{2} R_{out1} - V_{CMO1} - V_{th})^2$$

(5)

Finally, using (2), (5) the current through  $M_{20}$  is calculated:

$$I_{18} = \frac{\beta_{18}}{2} \left( \frac{\sqrt{2(\frac{\beta_{12}}{2}(V_{DD} - g_{meff} \frac{V_{id}}{2}R_{out1} - V_{CMO1} - V_{th})^{2})}}{\beta_{14}} + \frac{2(\frac{\beta_{12}}{2}(V_{DD} - g_{meff} \frac{V_{id}}{2}R_{out1} - V_{CMO1} - V_{th})^{2})}{\lambda_{16}\beta_{16}(V_{b4} - V_{th})^{2}} - \frac{1}{\lambda_{16}} \right) FOM_{s} = \frac{UGBW.C_{L}}{I_{T}}$$

$$FOM_{L} = \frac{SR.C_{L}}{I_{T}}$$

From (6), it is obvious that for a large  $V_{id}$  the output current increases proportional to  $V_{id}^4$ . That would enhance the SR of the OTA.

#### 3. Simulation Results

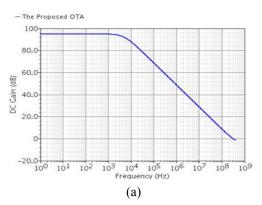

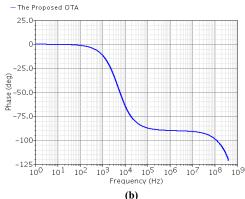

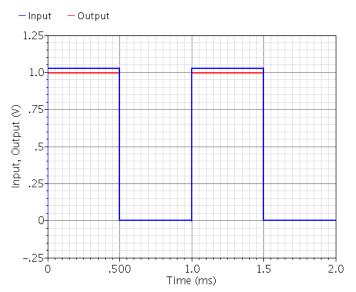

To verify the performance of the proposed two-stage class-AB OTA several simulations are performed in a 0.18  $\mu m$  CMOS process with 1.8V supply voltage using Cadence software. The specifications of the elements and bias voltages of the proposed OTA are reported in Table 1. The frequency responses of the proposed OTA are shown in Fig 3. According to the simulation results, The DC-gain of the OTA is 95 dB. UGBW and phase margin of the proposed OTA is 340 MHz and  $64^{\circ}$ , respectively. For the slew ratemeasurement, a square wave whit amplitude 1Vpp at 1 kHz wasapplied to the OTA and the result is given in Fig 4. The average SR of the OTA is 172 (V/ $\mu s$ ) .

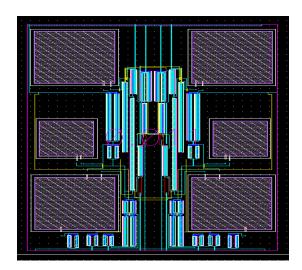

Complete OTA specifications along with a comparison to the conventional OTA are summarized in Table 2. The physical layout of the proposed OTA is shown in Fig 6. The layout area of the proposed OTA is 131µm×142µm.

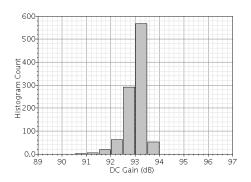

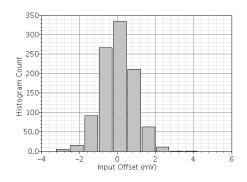

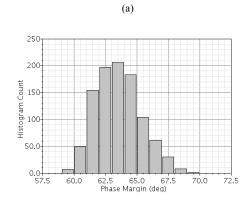

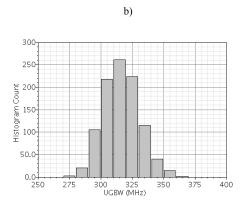

Monte Carlo (MC) simulations are done by considering both process and mismatch variations. Fig 5 demonstrates the MC histograms of the proposed OTA using 1000-run simulations. The vertical axis represents the histogram count. The horizontal axis in Figa to d represents the DC-gain, input offset, phase margin and UGBW, respectively.

The results are also summarized in Table 3. As can be seen from the results, under the process and mismatch variations the OTA specifications are not degraded significantly.post-layout simulation results are compared with some other methods in Table 4. Theproposed OTA shows the small value for layout area compared to the most existingmethods. Moreover, the results indicate that the proposed OTA has the highest DC-gain compared to the other techniques. It has the lowest input-referred noise due to the improved input stage trans-conductance. To compare the other performance parameters, the traditional couple of figures of merits in (7), (8) which for a given load indicate a trade-off between speed performance and total bias current  $V_{\rm DS,sat}$  are utilized [6-7]

$$FOM_s = \frac{UGBW.C_L}{I_T} \tag{7}$$

$$FOM_{L} = \frac{SR.C_{L}}{I_{T}} \tag{8}$$

As can be seen from Table 4, the proposed OTA has proper values for both of FOMs and  $FOM_L$ .

Fig 3. Frequency responses for both OTAs: (a) magnitude and (b) phase

Fig 4. Large signal step responses of the OTA

Table 1. The specifications of the elements and bias voltages of the proposed OTA

| Parameter                   | Value                      | Parameter         | Value         |

|-----------------------------|----------------------------|-------------------|---------------|

| $(W/L)_{1a,1b}$             | 1×10μm/0.18μm              | $(W/L)_{23a,23b}$ | ×15μm/0.18μm  |

| $(W/L)_{2a,2b}$             | 1×25μm/0.18μm              | $(W/L)_{24a,25a}$ | 1×45μm/0.18μm |

| $(W/L)_{3a,3b}$             | 2×25μm/0.18μm              | $(W/L)_{24b,25b}$ | ×15μm/0.18μm  |

| $(W/L)_{4a,4b,4c,4d}$       | 1×12.5μm/0.18μm            | $C_a, C_s$        | 2.1 pF        |

| $(W/L)_{5,6}$               | 1×15μm/0.18μm              | $C_{\mathrm{L}}$  | 10 pF         |

| $(W/L)_{7,8}$               | $1\times30\mu m/0.18\mu m$ | $V_{b1}$          | 0.63V         |

| $(W/L)_{9,10}$              | $1\times30\mu m/0.18\mu m$ | $V_{b2}$          | 0.77V         |

| $(W/L)_{11,12}$             | 2×15μm/0.36μm              | $V_{b3}$          | 1.15 <i>V</i> |

| $(W/L)_{13,14,15,16,17,18}$ | 2×10μm/0.36μm              | $V_{b^4}$         | 0.77V         |

| $(W/L)_{19,20}$             | 2×40μm/0.36μm              | $V_{cmo1}$        | 1.15 <i>V</i> |

| (W/L) <sub>21,22</sub>      | 2×10μm/0.36μm              | $V_{cmo2}$        | 0.9V          |

| Specification                                      | Conventional OTA |             |            | Proposed OTA |             |            |

|----------------------------------------------------|------------------|-------------|------------|--------------|-------------|------------|

| Specification                                      | TT( 27° C)       | FF( -40° C) | SS( 90° C) | TT( 27° C)   | FF( -40° C) | SS( 90° C) |

| Technology                                         | 0.18µm           | 0.18µm      | 0.18µm     | 0.18µm       | 0.18µm      | 0.18μm     |

| DC-Gain (dB)                                       | 74               | 69          | 71         | 95           | 88          | 96         |

| Input-Referred Noise@100kHz $(\mu V/\sqrt{Hz})$    | 0.55             | 0.44        | 0.95       | 0.21         | 0.19        | 0.30       |

| Differential output<br>Swing (peak to<br>peak) (V) | 2.8              | 2.8         | 2.8        | 2.8          | 2.8         | 2.8        |

| Phase Margin (°)                                   | 62               | 64          | 78         | 64           | 63          | 67         |

| Power Dissipation (mW)                             | 2.9              | 4.3         | 1.8        | 3            | 4.1         | 2.3        |

| Slew Rate                                          | 42               | 90          | 26         | 172          | 221         | 122        |

Table 2. Specifications of the proposed OTA and conventional OTAs.

(V/μs) UGBW (MHz)

$C_L(pF)$

(c) (d)

Fig 5. Histogram of MC Simulation. (a) Dc Gain, (b) Input Offset, (c) Phase Margin, (d) UGBW.

Specification

Mean Value

Standard Deviation

DC Gain (dB)

93.5

3.9

Input Offset (mV)

0.02

0.8

Phase Margin (°)

63.6

1.8

UGBW (MHz)

326.5

10.2

Table 3. The MC Analysis of the Proposed OTA.

Fig 6. Physical layout of the proposed OTA

Table <sup>£</sup>.Performance Comparison of the Proposed OTA and the Existing Methods

|                                                 | This <sup>a</sup><br>work | [12]  | [14]  | [17]   | [23] <sup>a</sup> |

|-------------------------------------------------|---------------------------|-------|-------|--------|-------------------|

| Technology                                      | 0.18µm                    | 0.5µm | 0.5µm | 0.18µm | 0.18µm            |

| Supply Voltage (V)                              | 1.8                       | 1     | 1     | 1.8    | 1.8               |

| DC-Gain (dB)                                    | 93.5                      | 30    | 76.8  | 72     | 93                |

| Input-Referred Noise@100kHz $(\mu v/\sqrt{Hz})$ | 0.23                      | 144   | 0.023 | 144    | 0.31              |

| Differential Output Swing (peak to peak) (V)    | 2.8                       |       | 1     | 1      | 2.8               |

| Phase Margin (°)                                | 64                        | 90    | 75.1  | 50     | 65                |

| Power Dissipation (mW)                          | 3                         | 0.08  | 0.1   | 11.9   | 3                 |

| Slew Rate (V/µs)                                | 172                       | 0.35  | 25.3  | 74.1   | 494               |

| UGBW (MHz)                                      | 334                       | 0.2   | 3.4   | 86.5   | 216               |

| Loading Capacitance (pF)                        | 10                        | 80    | 70    | 200    | 1                 |

| Operating Mode <sup>a</sup>                     | SI                        | SI    | SI    | SI     | SI                |

| $FOM_S = \frac{MHz.pF}{mA}$                     | 2000                      | 200   | 1190  | 2613   | 135               |

| $FOM_L = \frac{V.pF}{\mu s.mA}$                 | 1012                      | 350   | 8855  | 2239   | 309               |

## 3. Conclusion

In this paper, a new two-stage class-AB OTA in a 0.18  $\mu$ m CMOS process with a 1.8 V supply voltage has been presented. The proposed OTA was based on the simultaneous application of class-AB operation in both of the stages. Using active loads and also RFC structure, the first stage trans-conductance has been increased. The NLCM in the output stage has been employed to enhance the SR of the OTA. To evaluate the effectiveness of the proposed method, several simulations have been performed. The results indicated the better performance of the proposed OTA in terms of DC-gain, UGBW, and SR compared to the existing methods.

# References

- Ghosh, S., Bhadauria, V. (2021). High current efficiency single-stage bulk-driven subthresholdbiased class-AB OTAs with enhanced transconductance and slew rate for large capacitive loads, Analog Integrated Circuits and Signal Processing, 109, 403–433

- 2. Kumar, T. B., Kar, S. K., Boolchandani, D. (2020). A wide linear range CMOS OTA and its application in continuous-time filters, Analog Integrated Circuits and Signal Processing. 103, 283–290.

- 3. Wen, B., Zhang, Q., Zhao, X. (2019). A two-stage CMOS OTA with enhanced transconductance and DC-gain ,Analog Integrated Circuits and Signal Processing. 98, 257–264

- M.P. Garde, A.J. Lopez-Martin, R.G. Carvajal, J.A. Galan, J. Ramirez-Angulo, Super class AB RFC OTA using non-linear current mirrors, Electronics Letters. 54 (2018) 1317-1318.

- Kulej, T., Khateb, F. (2020). A Compact 0.3-V Class AB Bulk-Driven OTA, IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 28, 224-232.

- Pourashraf, S., Ramirez-Angulo, J., Roman-Loera, A., Gangineni, M. (2019). Gain and Bandwidth Enhanced Class-AB OTAs, IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS). 778-781.

- 7. Ferreira, L. H. C. ,Pimenta, T. C., Moreno, R. L. (2007) An ultra-low-voltage ultra-low-power CMOS Miller OTA with rail-to-rail input/output swing, IEEE Trans. Circuits Syst. II. 54, 843–847.

- 8. Raikos, G., Vlassis, S. (2011). Low-voltage bulk-driven input stage with improved transconductance, J. Circuit Theor.39, 39: 327–39.

- 9. Ferreira, L. H. C., Sonkusale, S. R. A. (2014). 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process, IEEE Trans. Circuits Syst. I, 61, 1609-1617.

- Thandri, B.K., et.al. (2003). A robust feedforward compensation scheme for multistage operational trans-conductance amplifiers with no Miller Capacitors, IEEE J. of Solid-State Circuits. 38, 237-243.

- 11. Callewaert L. andSansen, W. (1990). Class AB CMOS amplifiers with high efficiency, IEEE J. Solid-State Circuits. 25, 684–691.

- Galan, JA., López-Martín, AJ., Carvajal, RG., Ramírez-Angulo, J., Rubia-Marcos, C. (2007). Super class-AB OTAs with adaptive biasing and dynamic output current scaling, IEEE Transactions on Circuits and Systems I: Regular Papers. 54, 449-457.

- Lopez-Martin, A.J., Baswa, S., Ramirez-Angulo, J., Carvajal, R.G. (2005). Low-voltage Super Class AB CMOS OTA cells with very high slew rate and power efficiency, IEEE J. Solid-State Circuits. 40, 1068– 1077.

- 14. Garde, M.P., Lopez-Martin, A., Carvajal, R.G., et al. (2018). Super class AB recycling folded cascode OTA, IEEE J. Solid-State Circuits. 53, 2614–2623.

- 15. Garde, M.P., Lopez-Martin, A., Carvajal, R.G., et al. (2018). Super class AB RFC OTA with adaptive local common-mode feedback, Electron. Lett.

- Perez, A., Nithin, K., Bonizzoni, E., and Maloberti, F. (2009). Slew-rate and gain enhancement in two stage operational amplifiers, IEEE Circuits Syst. 2485–2488.

- Sutula, S., Dei, M., Terés, L., Serra-Graells, F. (2016). Variable-Mirror Amplifier: A New Family of Process-Independent Class-AB Single-Stage OTAs for Low-Power SC Circuits, IEEE Transactions on Circuits and Systems I: Regular Papers. 63, 1101-1110.

- Lopez-Martin, A., Algueta, J. M., Garde, M. P., Carvajal, R. G., & Ramirez-Angulo, J. (2020). 1-V 15-μW 130-nm CMOS Super Class AB OTA. IEEE International Symposium on Circuits and Systems (ISCAS), 1–4.

- 19. Roh, J. (2006). High-gain class-AB OTA with low quiescent current, Journal Analog Integr. Circuits Signal Process. 47, 225–228.

- Assaad, R., and Silva-Martinez, J. (2009). The recycling folded cascode: A general enhancement of the folded cascode amplifier, IEEE Journal. Solid-State Circuits. 44, 2535–2542.

- 21. Yavari, M., and Moosazadeh, T. (2014). A single-stage operational amplifier with enhanced transconductance and slew rate for switched-capacitor circuits, Journal. Analog Integr. Circuits Signal Process. 79, 589–598.

- 22. Yavari, M. (2005). Hybrid cascode compensation for two-stage CMOS op-amps, IEICE trans. Electronics. 88, 1161-1165.

- Anisheh, S. M., Shamsi, H. (2016). Two-stage class-AB OTA with enhanced DC gain and slew rate, International Journal of Electronics Letters. 5, 438-448.

- Guo, J., Ho, M., Kwong, KY., Leung, KN. (2015).

Power-area-efficient transient-improved capacitor-free FVF-LDO with digital detecting technique.

Electronics Letters . 51, 94–96.

- Pelgrom, M. J. M., Duinmaijer, A. C. J., Welbers, A. P. G. (1989). Matching Properties of MOS Transistors, IEEE Journal Solid-State Circuits. 24, 1433-1439.

- 26. Grasso, A. D., Palumbo, G., Pennisi, S. 2006. Three-stage CMOS OTA for large capacitive loads with efficient frequency compensation scheme, IEEE Trans. Circuits Syst. II, Exp. Briefs. 53, 1044-48.

- Grasso, A. D., Palumbo, G., Pennisi, S. 2007. Advances in reversed Nested Miller compensation. IEEE Trans. Circuits Syst. I, Reg. Papers. 45, 1459-1470.