# **RESEARCH ARTICLE**

# An innovative method for estimating optimal Gate work function and dielectric constant of a nanoscale DG-TFET based on analytical modeling of tunneling length in ambipolar, Off and ON states

Fayzollah Khorramrouz<sup>1</sup>, Seyed Ali Sedigh Ziabari<sup>1,\*</sup>, Ali Heydari<sup>3,4</sup>

<sup>1</sup> Department of Electrical Engineering, Rasht Branch, Islamic Azad University, Rasht, Iran

<sup>2</sup> Department of Electrical Engineering, Rasht Branch, Islamic Azad University, Rasht, Iran

Islamic Azad University of Rasht, Gaz Sq., Rasht, Iran

<sup>3</sup> Smartec B. V. The Netherland, Electronic Instrumentation Laboratory, Delft University of Technology, the Netherlands

<sup>4</sup> Department of Electrical Engineering, Guilan University, Rasht, Iran.

| ARTICLE INFO                                                                                  | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>Article History:</b><br>Received 2020-10-23<br>Accepted 2021-03-17<br>Published 2021-05-01 | In this paper, we propose an innovative and low computational cost approach<br>that can be used to find optimal values of parameters of a nanoscale dual gate<br>tunneling field-effect transistor (DG-TFET). In this way, after obtaining analytical<br>expressions for potential and energy bands of the device using the Poisson<br>equation, the tunneling length is extracted at source-channel and channel-drain<br>tunnel junctions in the AMBIPOLAR, Off and On states. Due to the tunneling |  |

| Keywords:                                                                                     | length equation, the different values of gate work function and dielectric constant                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2D Analytical model                                                                           | of the device are swept to determine the minimum and maximum design                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Surface potential                                                                             | limits. According to the above range, the necessary checks are made to reach                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| BTBT                                                                                          | the local optimal behaviors. These optimum points are explained based on the achievement of optimal device performance. The accuracy and consistency of the                                                                                                                                                                                                                                                                                                                                          |  |

| minimum tunneling                                                                             | proposed model is validated with the TCAD simulation results. The present model                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| length                                                                                        | can be a handful for the study of TFET performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| DG-TFET                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

#### How to cite this article

*Khorramrouz F., Sedigh Ziabari S.A., Heydari A. An innovative method for estimating optimal Gate work function and dielectric constant of a nanoscale DG-TFET based on analytical modeling of tunneling length in ambipolar, Off and ON states. J. Nanoanalysis., 2021; 8(2): 112-121. DOI: 10.22034/jna.003.*

### INTRODUCTION

Scaling of conventional CMOS transistors according to Moore's law is facing several challenges, such as high OFF-state current, high sub-threshold slope (SS) and other short channel effects (SCEs). The above-mentioned causes poor operation of the device and high power consumption in chips[1–5]. Hence, the proposal of a new device is inevitable. The tunneling field-effect transistor (TFET) is a decent choice because of energy efficiency and lower sub-threshold slope (SS) [6–8]. The major weaknesses of TFETs are low drain current due to poor band to band tunneling rate and conduction in the positive and negative voltages of the gate (ambipolarity). Several studies have been conducted to overcome these shortcomings that are beyond the scope of this paper [9–14]. One of the main areas of research in the field of semiconductor devices is analytical modeling. Analytical modeling can be useful in the rapid and low-cost evaluation of semiconductor devices. It is also used to offer a model for simulator software [15,16]. Some researchers proposed analytical modeling for TFET using the MOSFET model [17]. Many researchers study the Sub-threshold swing and the threshold voltage of TFET [18,19].

\* Corresponding Author Email: sedigh@iaurasht.ac.ir

Several analytical studies try to offer a 2-D

**This work is licensed under the Creative Commons Attribution 4.0 International License.** To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

or 3-D expression for TFETs with or without considering the impact of the depletion region, mobile charge and drain voltage. Many 2-D studies on TFET modeling analytically calculate the tunneling generation rate using a 2-D electric field and Some studies emphasize the modeling of different physical structures of the device[19-24]. While some other researchers consider device modeling according to the type of insulator and shape and number of gates. Investigating the performance of the TFETs by using the analytical modeling also did not exclude the attention of researchers. Many attempts have focused on analytical modeling of junction-less TFETs [25]. In this paper, we start with the modeling of the surface potential along the channel using a pseudo-2D model [26] considering the depletion regions at source-channel and channel drain junction. We then find the smallest tunneling length which is very essential to finding drain current and in our proposed method. The method presented in this paper is to find the proper values of the workfunction of the gate and the dielectric constant with respect to the tunneling length. We derive the tunneling length for AMBIPOLAR, OFF and ON state at different values of the gate work-function and dielectric constant using our proposed method. The two-dimensional curve obtained from this step is analyzed in order to obtain the appropriate

values of the parameters. The method of analysis is a combination of qualitative analysis, evaluation of maximum or minimum points of the curves, and also referring to the TCAD simulation results. We believe that this method while avoiding complex optimization procedures is useful in achieving the desired device efficiency. A 2-D dimensional numerical simulation validates accuracy of the proposed model.

The rest of the paper is organized as follows: In section 2, device structure and analytical modeling of surface potential will be discussed. The tunneling length in AMBIPOLAR, OFF and ON state also will be presented in section 3. The validation of our proposed method also is described in Section 4. Results and discussions and finally the conclusion will be presented in sections 5 and 6 respectively.

## MATERIALS AND METHODS

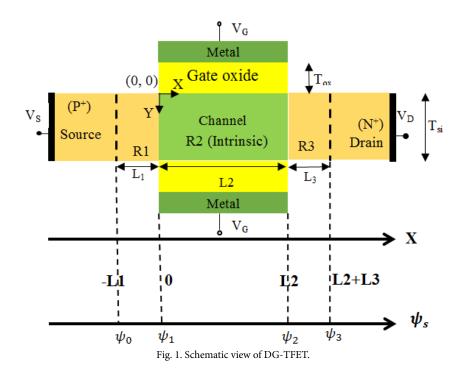

Fig. 2. shows a 2-D structure of a dual gate tunneling field-effect transistor (DG-TFET). The total gate length is L2. The silicon body and oxide thicknesses are  $T_{si}$  and  $T_{ox}$  respectively. The Source and the drain are highly doped with p and n-type dopant at a concentration of N1 and N3. The channel region is lightly doped with N2. Regions R1, R2 and R3 demonstrate depletion region at the source side, channel region under the gate and drain side depletion region respectively. L1 and

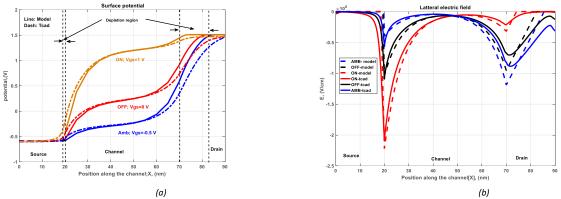

Fig. 2. Surface potential of DG-TFET (a) and Lateral electric field (b) for ON state:  $V_{gs} = 1 V$  and  $V_{ds} = 1 V$ ; OFF state:  $V_{gs} = 0 V$  and  $V_{ds} = 1 V$ . V and AMBIPOLAR state:  $V_{gs} = -0.5 V$  and  $V_{ds} = 1 V$ .

Table 1. Device design and material parameters.

| Parameter name               | Symbol          | Value               | unit             |

|------------------------------|-----------------|---------------------|------------------|

| Gate oxide thickness         | T <sub>ox</sub> | 3                   | nm               |

| Silicon body thickness       | $T_{si}$        | 12                  | nm               |

| Source doping concentration  | $N_1$           | $1 \times 10^{20}$  | cm <sup>-3</sup> |

| Channel doping concentration | $N_2$           | $1 \times 10^{16}$  | cm <sup>-3</sup> |

| Drain doping concentration   | $N_3$           | $-5 \times 10^{18}$ | cm <sup>-3</sup> |

| Metal work-function          | $\phi_m$        | 4.5                 | eV               |

| Source region length         | $L_S$           | 20                  | nm               |

| Gate length                  | $L_{s}$         | 50                  | nm               |

| Drain region length          | $L_{l}$         | 20                  | nm               |

| Dielectric constant          | Eox             | 3.9                 | -                |

L3 are depletion region length. The other Physical characteristics of the device are listed in Table 1

# 2-D Poisson's Equation in the Channel

Neglecting the mobile charge, the 2-D Poisson's equation in the channel region of the device is given by[27]:

$$\frac{\partial^2 \psi_2(x, y)}{\partial x^2} + \frac{\partial^2 \psi_2(x, y)}{\partial x^2} = \frac{qN_2}{\varepsilon_{Si}}$$

(1)

Where  $\Psi_2(x, y)$  demonstrates the 2-D electrostatic potential in the channel, q is the electronic charge,  $\mathcal{E}_{Si}$  is the permittivity of silicon and N<sub>2</sub> is the channel concentration. The potential distribution along the channel can be approximated by the second-order polynomial as [28–34]:

$$\psi_{2}(x, y) = a_{0}(x) + a_{1}(x)y + a_{2}(x)y^{2}$$

(2)

Where  $a_0$ ,  $a_1$  and  $a_2$  are channel length-

dependent obtained from properly defined boundary conditions. Using boundary conditions, the surface potential of the channel  $\Psi_{s2}(x)$  can be found as:

$$\psi_{2}(x,y) = \psi_{s2}(x) + \frac{C_{ox}(V_{GS} - \emptyset_{ms} - \psi_{s}(x))}{\varepsilon_{Si}} \times y - \frac{C_{ox}(V_{GS} - \emptyset_{ms} - \psi_{s}(x))}{\varepsilon_{Si}} \times y^{2}$$

(3)

Where,  $C_{ox} = \varepsilon_{ox}/T_{ox}$  and  $\emptyset_{ms} = \emptyset_{metal} - \emptyset_{Si}$  are oxide capacitance and metal-silicon work-function difference.  $\emptyset_{Si}$  Is the silicon work-function as  $\chi + E_g/2q$ , where  $\chi$  is the electron affinity of the silicon. Substituting (3) in (1) yields the following1-D second orders differential equation:

$$\frac{d^2\psi_{s2}(x)}{dx^2} + K^2\psi_{s2}(x) = \sigma$$

(4)

Where

J. Nanoanalysis., 8(2): 112-121, Spring 2021

$$K = \sqrt{\frac{2C_{ox}}{\varepsilon_{Si} - T_{Si}}}; \ \sigma = \frac{qN_2}{\varepsilon_{Si}} + \frac{2C_{ox}}{\varepsilon_{Si} - T_{Si}} V_{GS}; \ \text{and} \ V_{GS} = V_{GS} - \mathcal{O}_{ms}$$

(5)

The general and particular solution of (4) is:

$$\sigma_{s2}(\mathbf{x}) = A_2 \exp(\mathbf{K}\mathbf{x}) + B_2 \exp(-\mathbf{K}\mathbf{x}) + \xi;$$

$$\xi = \sigma / K^2$$

(6)

Hence using the potential continuity in the interfaces of two consecutive regions, the coefficients of (6) are:

$$A_{2} = \frac{-1}{2\sinh(KL_{2})} \Big[ (\psi_{1} - \xi) \exp(-KL_{2}) - (\psi_{2} - \xi) \Big]$$

(7)

$$B_{2} = \frac{-1}{2\sinh(KL_{2})} \Big[ (\psi_{2} - \xi) - (\psi_{1} - \xi) \exp(KL_{2}) \Big]$$

(8)

The interface potential of  $\psi_1$  and  $\psi_2$  are derived using the continuity of potential and electric field which will be discussed later.

### Poisson's Equation in the Depletion regions

The precise modeling of channel potential involves the consideration of drain and source depletion regions. As is obtained from the TCAD simulation and according to report [35], the major changes in surface potential of region R1 and R2 are along the channel, therefore, we solve the Poisson equation in these regions one-dimensionally. The 1-D Poisson's equation inside the depletion regions of the device is expressed as:

$$\frac{d^2 \psi_{s1}(x)}{dx^2} = \frac{qN_1}{\varepsilon_{si}}; \quad -L_1 \le x \le 0$$

(9)

$$\frac{d^2 \psi_{s3}(x)}{dx^2} = -\frac{qN_3}{\varepsilon_{Si}}; \quad 0 \le x \le L_2 + L_3$$

(10)

Twice integrating the (9)-(10), we get the following expression for  $\psi_{s1}(x)$  and  $\psi_{s3}(x)$  given by:

$$\psi_{s1}(x) = \frac{qN1}{2\varepsilon_{si}}(x+L_1)^2 + A_1(x+L_1) + B_1$$

(11)

$$\psi_{s3}(x) = -\frac{qN3}{2\varepsilon_{si}}(x - L_2)^2 + A_3(x - L_2) + B_3$$

(12)

The extension of the depletion region in the source is as far as the electrostatic potential becomes a constant value of  $\psi_n = \frac{K_n T_n N!}{q}$  which is called builtin potential ( $\psi_0$ ). At this point, the electric field will be zero. Meanwhile, the extension of the depletion region in the drain side is as high as the potential reaches the value of  $\psi_1 = \frac{K_n T}{q} ln \frac{N^3}{n_e} + V_n$  and the electric field becomes zero. ( $K_B$  is the Boltzmann constant). Using the above-mentioned boundary conditions the other coefficients are as follows:

$$A_{1} = \frac{(\psi_{1} - \psi_{0}) - \frac{qN_{1}}{2\varepsilon_{s_{i}}} \times L_{1}^{2}}{L_{1}}$$

(13)

$$A_{3} = \frac{(\psi_{3} - \psi_{2}) + \frac{qN3}{2\varepsilon_{s_{i}}} \times L_{3}^{2}}{L_{3}}$$

(14)

$$B_3 = \psi_2 \tag{15}$$

And the depletion region length at source and drain side will be derived using the value of the electric field at  $x = -L_1$  and  $x = L_2 + L_3$  as:

$$E_{1}(x) = \frac{\partial \psi_{s1}(x)}{\partial x} \bigg|_{x=-L_{1}} = 0$$

(16)

$$E_3(x) = \frac{\partial \psi_{s3}(x)}{\partial x} \bigg|_{x=L_2+L_3} = 0$$

(17)

Solving equations (16)-(17) yields depletion region length as:

$$L_{1} = \sqrt{2\varepsilon_{Si}\left(\psi_{1} - \psi_{0}\right)/qN1}$$

(18)

$$L_3 = \sqrt{2\varepsilon_{Si}\left(\psi_3 - \psi_2\right)/qN3} \tag{19}$$

The intermediate potential  $(\psi_1 and \psi_2)$  can be calculated using the continuity of potential at channel-source and channel-drain interfaces as:

$$\psi_{s1}|_{x=0} = \psi_{s2}|_{x=0} \Longrightarrow \frac{q_{N1}}{2\varepsilon_{s1}} (L_1)^2 + A_1(L_1) + B_1 = A_2 + B_2 + \xi$$

(20)

$$\psi_{s2}|_{x=L_2} = \psi_{s3}|_{x=L_2} \Rightarrow A_2 \exp(KL_2) + B_2 \exp(-KL_2) + \xi = B_3(21)$$

J. Nanoanalysis., 8(2): 112-121, Spring 2021

#### F. Khorramrouz et al. / An innovative method for estimating optimal Gate work

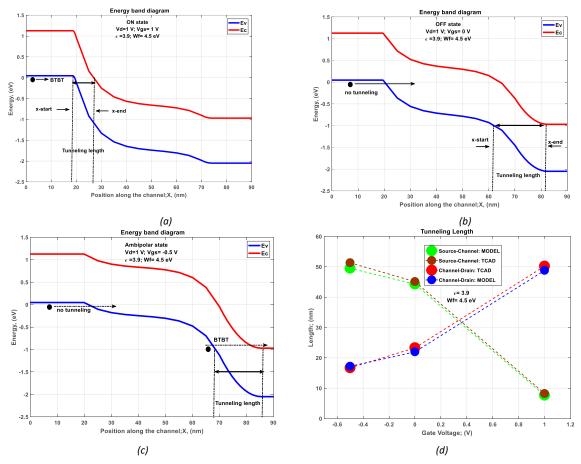

Fig. 3. Source-channel and Channel-Drain tunneling length of DG-TFET for AMBIPOLAR, OFF and ON state (a); Energy band diagram in the ON state (b); OFF state (c) and AMBIPOLAR state (d).

We find  $\psi_1, \psi_2$  from above-mentioned system of nonlinear equations.

## Tunneling length

The tunneling length is the physical path through which the band to band tunneling occurs. This path occurs in the ON, OFF and the AMBIPOLAR state. The difference is in the tunneling region and hence the starting and endpoint. The tunneling length is a path between the two equal potential points. To understand and analyze the tunneling length, we need the energy band diagram in different biasing conditions[36, 37] as:

$$E_{C}(x) = -\psi_{s}(x) + \frac{E_{g}}{2} , \quad E_{V}(x) = -\psi_{s}(x) - \frac{E_{g}}{2}$$

(22)

The surface potential of the DG-TFET is shown

in Fig. 2(a) for ON, OFF and AMBIPOLAR state. As we expect, an extension of the depletion region at the drain side is more because of higher reverse bias in this side. The lateral electric field is shown in Fig. 2(b). A good agreement between the model and TCAD results is seen.

### Source-Channel Junction Tunneling length

The energy band diagram of the DG-TFET in the ON state is shown in Fig. 3(a). The closure of the Fermi level with the valence band of the source to the corresponding point in the conduction band of the channel is the minimum tunneling length. However, because of the high level of doping in the source, the difference between the Fermi and valence band can be ignored. Thus, the tunneling starts from the junction of the depletion region with the source and ends in a point in the channel conduction band which the energy value of the start and endpoints of the tunneling is equal. Accordingly, one can write:

$$E_{V-Source}(x)\Big|_{x=x_{start}} = E_{C-Channel}(x)\Big|_{x=x_{end}}$$

(23)

$$\left(-\psi_0 - \frac{E_g}{2}\right) = \left(-\psi_{S2}\left(x\right) + \frac{E_g}{2}\right)$$

(24)

Using (6) and  $x_{start} = -L_1$  from (18), the tunneling length in the ON state is expressed as follow:

$$L_{Source-Channel} = \frac{Log\left(\frac{-(\xi - \psi_0 - E_s) + \sqrt{(\xi - \psi_0 - E_s)^2 - 4A_2B_2}}{2A_2}\right)}{K} - L_1$$

(25)

#### *Channel-Drain Junction Tunneling length*

The energy band alignment between the channel valence band and the drain conduction band is also observed for OFF and Ambipolar state. The energy band diagram in the OFF and the Ambipolar state is shown in Fig. 3(b) and Fig. 3(c) respectively. The tunneling path starts from the channel valence band and ends to drain conduction band. The endpoint is the end of the depletion region extension at the drain side. To achieve the main equation, it is enough to equal the amount of energy at the start and endpoints of the tunneling, as below:

$$E_{V-Channel}(x)\Big|_{x=x_{start}} = E_{C-CDrain}(x)\Big|_{x=x_{end}}$$

(26)

$$\left(-\psi_{s2}\left(x\right)-\frac{E_g}{2}\right) = \left(-\psi_3 + \frac{E_g}{2}\right)$$

(27)

Using (6) and (12) one can write:

$$L_{Channel-Drain} = (L_2 + L_3) - \frac{Log\left(\frac{-(\xi - E_{end} + E_g) + \sqrt{(\xi - E_{end} + E_g)^2 - 4A_2B_2}}{2A_2}\right)}{K}$$

(28)

Where

$$E_{end} = \left(-\frac{qN3}{2\varepsilon_{Si}}\left(L_3\right)^2 + A_3\left(L_3\right) + B_3\right)$$

(29)

The method for calculating the tunneling length in the Ambipolar state is exactly the same as the OFF state because the tunneling phenomenon occurs in the same region Fig. 3(c).

## Model validation

The accuracy of the proposed model is verified by comparing the numerical modeling results with 2D numerical simulations. SILVACO ATLAS 2D 5.19.20 R is employed for all simulations. The models used include Shockley Read Hall (SRH) and Auger (AUGER) recombination models, Fermi-Dirac statistics and band-gap narrowing model (BGN) [45–47].

## **RESULTS AND DISCUSSIONS**

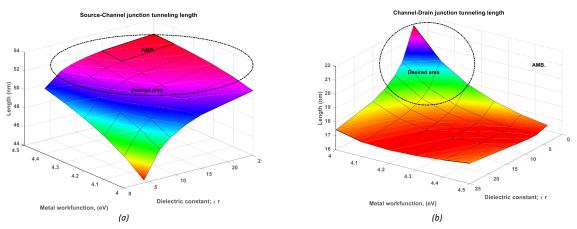

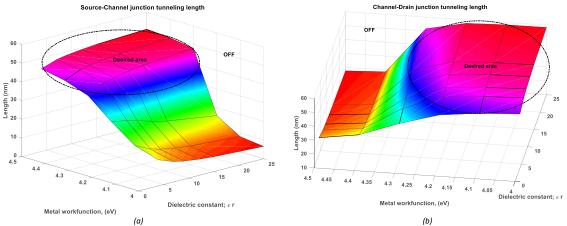

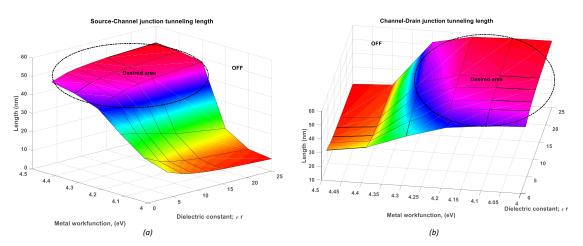

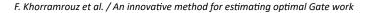

The tunneling length at Source-Channel and Channel-Drain junction at Ambipolar, OFF and ON state is shown in Fig. 3(d). Good consistency between the model and TCAD is observed. After extracting an expression for tunneling length, we assign the different values of the gate work-function and the dielectric constant of the insulator. The result is a three-dimensional graph, which can be used to evaluate the performance of the device. The purpose of this assessment is to reach the optimal local points for the least OFF and Ambipolar current and the highest ON current. It should be noted that the basis of our judgment is the tunneling length in each case. The three-dimensional curves of the tunneling length in the source and drain side junction for various states are shown in Fig. 4. -Fig. 6. The preliminary study of 3D curves can be summarized as follows:

1. In the Ambipolar state, the tunneling length in the channel-drain junction is maximal when the work-function is equal to 4 eV (Fig. 4(b)). On the other hand, this amount of work-function minimizes the tunneling length at the source side, which is undesirable (Fig. 4(a)). Therefore, the work-function must be selected in such a way that both tunneling lengths are in the optimal position. Therefore, the intermediate values of the work-function, (e.g. 4.2 or 4.3 eV), are suggested.

2. In the OFF state, tunneling in the sourcechannel junction is more influenced by the gate work-function than the dielectric constant (Fig. 5(a)). In other words, it is necessary to avoid the lower values of the work-function. At the same time, the lower value of the gate work-function reduces the tunneling length in the channel-drain junction (Fig. 5(b)), which is not at all desirable.

Fig. 4. The effect of dielectric constant and gate work-function on tunneling length of Source-Channel junction (a) and Channel-Drain junction (b) in the AMBIPOLAR state ( $V_{ds}$ =1 V and  $V_{gs}$ =-0.5 V).

Fig. 5. The effect of dielectric constant and gate work-function on tunneling length of Source-Channel junction (a) and Channel-Drain junction (b) in the OFF state ( $V_{ds}=1 V$  and  $V_{gs}=0 V$ ).

Fig. 6. The effect of dielectric constant and gate work-function on tunneling length of Source-Channel junction (a) and Channel-Drain junction (b) in the ON state ( $V_{ds}=1 V$  and  $V_{gs}=1 V$ ).

J. Nanoanalysis., 8(2): 112-121, Spring 2021

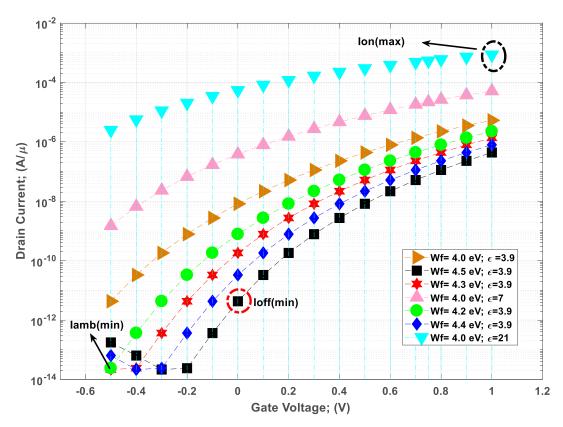

Fig. 7. Drain current of DG-TFET extracted from our model and SILVACO TCAD simulation tool.

Therefore, the higher values of the work-function are preferable. Taking into account simultaneously the realities associated with the tunneling length in the source-channel and channel-drain junction, the higher values of the work-function can be an optimal choice to keep the OFF current down.

3. In the ON state, the tunneling length in the channel-drain is so high that there is no band to band tunneling in this junction (Fig. 6(b)). In other words, the dielectric constant and the work-function do not interfere in the tunneling of this junction. Meanwhile, the effect of dielectric constant on the source-channel junction tunneling length is more than work-function (Fig. 6(a)). Therefore, selecting high values of dielectric constant reduces the tunneling length and, as a result, increases the drain current ( $I_{ON}$ ).

In order to verify our proposed method, we examine the values of the gate work-function as well as the dielectric constant corresponding to each of the optimal states in the TCAD. The drain current corresponding to each of the above states is shown in Fig. 7. According to the above, high dielectric constant values with any value of workfunction can improve the ON current. This is clearly shown in (Fig. 7) for (Wf=4 eV;  $\varepsilon_r$ =7) and (Wf=4 eV;  $\varepsilon_r$ =21). In these two samples, we have the highest ON current. In the case where the work unction is selected in range 4.2 eV to 4.3 eV, the Ambipolar current is very low. Also, with a workfunction equal to 4.5 eV, the minimum OFF current is achievable.

## CONCLUSION

The idea of analytical modeling of DG-TFET can extract a closed-form formula for tunneling length in source-channel and channel-drain junctions. From the perspective of the energy band diagram, surface potential and, lateral electric field, the model corresponds well to the simulation results. To achieve optimal conditions, simultaneous effects of different values of the gate work-function and dielectric constant on the tunneling length in Ambipolar, OFF and ON state have been investigated which has a good agreement with simulation results. Based on the results, the allowable values of the gate work-function and dielectric constant are determined according to the principles of minimum Ambipolar and OFF current and maximum ON current. The simulation results confirm the correctness of this proposal.

## **CONFLICT OF INTEREST**

All authors declare that no conflicts of interest exist for the publication of this manuscript.

#### REFERENCES

- G. Brown, P. Zeitzoff, G. Bersuker, H. Huff, Scaling CMOS: Materials & Amp; devices, Mater. Today. 7 (2004) 20–25. doi:10.1016/S1369-7021(04)00051-3.

- [2] M.T. Bohr, I.A. Young, CMOS Scaling Trends and Beyond, IEEE Micro. 37 (2017) 20–29. doi:10.1109/ MM.2017.4241347.

- [3] T. Skotnicki, J.A. Hutchby, T.J. King, H.S.P. Wong, F. Boeuf, The end of CMOS scaling: Toward the introduction of new materials and structural changes to improve MOSFET performance, IEEE Circuits Devices Mag. 21 (2005) 16–26. doi:10.1109/MCD.2005.1388765.

- [4] L.C. Chen, M.S. Yeh, K.W. Lin, M.H. Wu, Y.C. Wu, Junctionless poly-si nanowire FET with gated raised S/D, IEEE J. Electron Devices Soc. 4 (2016) 50–54. doi:10.1109/ JEDS.2016.2514478.

- [5] A.S. Zoolfakar, N.I.M. Tahiruddin, L.N. Ismail, CMOS Devices, 2 (2009) 1–6.

- [6] N. Bagga, A. Kumar, A. Bhattacharjee, S. Dasgupta, Performance Evaluation of a Novel GAA Schottky Junction (GAASJ) TFET with Heavily Doped Pocket, Superlattices Microstruct. 109 (2017) 545–552. doi:10.1016/J. SPMI.2017.05.040.

- [7] P. Bal, B. Ghosh, P. Mondal, M.W. Akram, B.M.M. Tripathi, Dual material gate junctionless tunnel field-effect transistor, J. Comput. Electron. 13 (2014) 230–234. doi:10.1007/ s10825-013-0505-4.

- [8] P. Banerjee, S.K. Sarkar, 3-D analytical modeling of high-k gate stack dual-material tri-gate strained siliconon-nothing MOSFET with dual-material bottom gate for suppressing short channel effects, J. Comput. Electron. 16 (2017) 631–639. doi:10.1007/s10825-017-1002-y.

- [9] M.G. Bardon, H.P. Neves, R. Puers, C. Van Hoof, Pseudotwo-dimensional model for double-gate tunnel FETs considering the junctions depletion regions, IEEE Trans. Electron Devices. 57 (2010) 827–834. doi:10.1109/ TED.2010.2040661.

- [10] S. Chander, S. Baishya, Two-dimensional model of a heterojunction silicon-on-insulator tunnel field effect transistor, Superlattices Microstruct. 90 (2016) 176–183. doi:10.1016/J.SPMI.2015.12.013.

- [11] S. Garg, S. Saurabh, Suppression of ambipolar current in tunnel FETs using drain-pocket: Proposal and analysis, Superlattices Microstruct. (2017). doi:10.1016/J. SPMI.2017.11.002.

- [12] H. Aghandeh, S.A. Sedigh Ziabari, Gate engineered heterostructure junctionless TFET with Gaussian doping profile for ambipolar suppression and electrical performance improvement, Superlattices Microstruct. 111 (2017) 103–114. doi:10.1016/j.spmi.2017.06.018.

- [13] D.B. Abdi, M. Jagadesh Kumar, Controlling Ambipolar Current in Tunneling FETs Using Overlapping Gate-on-Drain, IEEE J. Electron Devices Soc. 2 (2014) 187–190. doi:10.1109/JEDS.2014.2327626.

- [14] Hraziia, A. Vladimirescu, A. Amara, C. Anghel, An analysis on the ambipolar current in Si double-gate tunnel FETs, in: Solid. State. Electron., Pergamon, 2012: pp. 67–72. doi:10.1016/j.sse.2011.11.009.

- [15] N.D. Chien, C.-H. Shih, Short channel effects in tunnel field effect transistors with different configurations of abrupt and graded Si/SiGe heterojunctions, Superlattices Microstruct. 100 (2016) 857–866. doi:10.1016/J.SPMI.2016.10.057.

- [16] W.Y. Choi, B.G. Park, J.D. Lee, T.J.K. Liu, Tunneling field effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec, IEEE Electron Device Lett. 28 (2007) 743–745. doi:10.1109/LED.2007.901273.

- [17] D.K. Dash, P. Saha, S.K. Sarkar, Analytical modeling of asymmetric hetero-dielectric engineered dual-material DG-TFET, J. Comput. Electron. 17 (2018) 181–191. doi:10.1007/s10825-017-1102-8.

- [18] S. Dash, B. Jena, G.P. Mishra, A new analytical drain current model of cylindrical gate silicon tunnel FET with source δ-doping, Superlattices Microstruct. 97 (2016) 231–241. doi:10.1016/J.SPMI.2016.06.018.

- [19] S. Dash, G.P. Mishra, A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET), Superlattices Microstruct. 86 (2015) 211–220. doi:10.1016/j. spmi.2015.07.049.

- [20] S. Dash, G.P. Mishra, A 2D analytical cylindrical gate tunnel FET (CG-TFET) model: Impact of shortest tunneling distance, Adv. Nat. Sci. Nanosci. Nanotechnol. 6 (2015) 035005. doi:10.1088/2043-6262/6/3/035005.

- [21] S. Marjani, S.E. Hosseini, R. Faez, A 3D analytical modeling of tri-gate tunneling field effect transistors, J. Comput. Electron. 15 (2016) 820–830. doi:10.1007/s10825-016-0843-0.

- [22] A.M. Ionescu, H. Riel, Tunnel field effect transistors as energy-efficient electronic switches, Nature. 479 (2011) 329–337. doi:10.1038/nature10679.

- [23] A.N. Hanna, H.M. Fahad, M.M. Hussain, InAs/Si heterojunction nanotube tunnel transistors, Sci. Rep. 5 (2015) 9843. doi:10.1038/srep09843.

- [24] Y. Goswami, P. Asthana, B. Ghosh, Nanoscale III–V on Si-based junctionless tunnel transistor for EHF band applications, J. Semicond. 38 (2017) 054002. doi:10.1088/1674-4926/38/5/054002.

- [25] S. Kumar, B. Raj, Compact channel potential analytical modeling of DG-TFET based on Evanescent-mode approach, J. Comput. Electron. 14 (2015) 820–827. doi:10.1007/s10825-015-0718-9.

- [26] R. Vishnoi, M.J. Kumar, A pseudo-2-D-analytical model of dual material gate all-around nanowire tunneling FET, IEEE Trans. Electron Devices. 61 (2014) 2264–2270. doi:10.1109/ TED.2014.2321977.

- [27] D. Roy, A. Biswas, Analytical model of nanoscale junctionless transistors towards controlling of short channel effects through source/drain underlap and channel thickness engineering, Superlattices Microstruct. 113 (2018) 71–81. doi:10.1016/J.SPMI.2017.09.056.

- [28] D. Maier, M. Alomari, N. Grandjean, J.F. Carlin, M.A. Diforte-Poisson, C. Dua, S. Delage, E. Kohn, InAlN/ GaN HEMTs for operation in the 1000 ??c regime: A first

experiment, IEEE Electron Device Lett. 33 (2012) 985–987. doi:10.1109/LED.2012.2196972.

- [29] Z. Ramezani, A.A. Orouji, Dual metal gate tunneling field effect transistors based on MOSFETs: A 2-D analytical approach, Superlattices Microstruct. 113 (2018) 41–56. doi:10.1016/J.SPMI.2017.09.042.

- [30] S. Dash, G.P. Mishra, A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET), Superlattices Microstruct. 86 (2015) 211–220. doi:10.1016/J. SPMI.2015.07.049.

- [31] A. Saeidi, A. Biswas, A.M. Ionescu, Modeling and simulation of low power ferroelectric non-volatile memory tunnel field effect transistors using silicon-doped hafnium oxide as gate dielectric, Solid. State. Electron. 124 (2016) 16–23. doi:10.1016/j.sse.2016.07.025.

- [32] S. Singh, B. Raj, S.K. Vishvakarma, Analytical modeling of split-gate junction-less transistor for a biosensor application, Sens. Bio-Sensing Res. 18 (2018) 31–36. doi:10.1016/j.sbsr.2018.02.001.

- [33] S. Mohammadi, H.R.T. Khaveh, An analytical model for double-gate tunnel FETs considering the junctions depletion regions and the channel mobile charge carriers, IEEE Trans. Electron Devices. 64 (2017) 1268–1276. doi:10.1109/TED.2017.2655102.

- [34] R. Hosseini, N. Teimourzadeh, M. Fathipour, A new source heterojunction strained channel structure for ballistic gate all around nanowire transistor, J. Comput. Electron. 13 (2014) 170–179. doi:10.1007/s10825-013-0496-1.

- [35] D. Keighobadi, S. Mohammadi, Physical and analytical

modeling of drain current of double-gate heterostructure tunnel FETs, Semicond. Sci. Technol. 34 (2019) 015009. doi:10.1088/1361-6641/aaeeeb.

- [36] R. Vishnoi, M.J. Kumar, 2-D analytical model for the threshold voltage of a tunneling FET with localized charges, IEEE Trans. Electron Devices. 61 (2014) 3054–3059. doi:10.1109/TED.2014.2332039.

- [37] R. Vishnoi, M.J. Kumar, Compact analytical model of dual material gate tunneling field-effect transistor using interband tunneling and channel transport, IEEE Trans. Electron Devices. 61 (2014) 1936–1942. doi:10.1109/ TED.2014.2315294.

- [38] M. Rahimian, M. Fathipour, Junctionless nanowire TFET with built-in N-P-N bipolar action: Physics and operational principle, J. Appl. Phys. 120 (2016). doi:10.1063/1.4971345.

- [39] Ajay, R. Narang, M. Saxena, M. Gupta, Two-dimensional (2D) analytical investigation of an n-type junctionless gateall-around tunnel field-effect transistor (JL GAA TFET), J. Comput. Electron. 17 (2018) 1–11. doi:10.1007/s10825-018-1151-7.

- [40] R. Ambika, N. Keerthana, R. Srinivasan, Realization of Silicon nanotube tunneling FET on junctionless structure using single and multiple gate workfunction, Solid. State. Electron. 127 (2017) 45–50. doi:10.1016/j. sse.2016.10.037.

- [41] Y. Liu, J. He, M. Chan, C.X. Du, Y. Ye, W. Zhao, W. Wu, W.L. Deng, W.P. Wang, An analytic model for gate-all-around silicon nanowire tunneling field effect transistors, Chinese Phys. B. 23 (2014). doi:10.1088/1674-1056/23/9/097102.