https://doi.org/10.30495/jce.2024.2000184.1235

#### Vol. 14/ No. 54/Winter 2025

**Research Article**

# Efficient Design of Parity-Preserving Reversible Non-Restoring Divider

Mohammad Talebi, Ph.D. Student<sup>1</sup> <sup>[D]</sup> Mohammad Mosleh, Associate Professor<sup>2\*</sup> <sup>[D]</sup> Mohsen Chekin, Assistant Professor<sup>3</sup> <sup>[D]</sup>

<sup>1</sup>Department of Computer Engineering, Dezful Branch, Islamic Azad University, Dezful, Iran, mtalebi@iaud.ac.ir

<sup>2</sup>Department of Computer Engineering, Dezful Branch, Islamic Azad University, Dezful, Iran, Mohammad.Mosleh@iau.ac.ir

<sup>3</sup>Department of Computer Engineering, Dezful Branch, Islamic Azad University, Dezful, Iran, Chegin@iaud.ac.ir

**Correspondence** Mohammad Mosleh, Associate Professor of Computer Engineering, Dezful Branch, Islamic Azad University, Dezful, Iran, Mohammad.Mosleh@iau.ac.ir

Received: 31 October 2023 Revised: 1 January 2024 Accepted: 15 January 2024

#### Abstract

One of the basic challenges in high-density integrated circuits is loss of power consumption, which is caused by presence of transistors in circuits and causes the temperature of the circuit to increase. The design of digital circuits in a reversible way can be used as one of efficient approaches to solve this challenge. In addition, the design of parity-preserving reversible circuits can be very effective in detecting faults in circuits. Dividers are used as one of the most widely used circuits in digital computing systems. Divider circuits include an adder, a multiplexer and two sequential register and parallel-in to parallel-out left shift register circuits. This paper is presented a new and efficient design of a parity-preserving reversible non-restoring divider. For this purpose, first, a parity-preserving reversible D-latch is proposed. second, a parity-preserving reversible n-bit register is presented using the proposed reversible D-latch. Third, a parity-preserving reversible (n+1) bit shift register using the proposed reversible D-latch and other reversible gates is proposed. Finally, a parity-preserving reversible n bit divider is developed based on the non-restoring algorithm. The results of comparisons show that the proposed circuit is superior in terms of evaluation criteria of reversible circuits such as quantum cost, number of constant inputs and number of garbage outputs compared to previous works.

**Keywords**: Divider, non-restoring algorithm, Parity-preserving reversible circuit, Quantum computing, Reversible logic.

#### Highlights

- Proposing a reversible D-latch memory with parity preserving ability.

- Introducing a reversible register with parity preserving ability.

- Providing a parity preserving reversible left-shift register with parallel load capability (PIPO).

- Development of an efficient parity preserving reversible non-restoring divider using the proposed circuits.

**Citation:** M. Talebi, M. Mosleh, and M. Chegin, "Efficient Design of Parity-Preserving Reversible Non-Restoring Divider," *Journal of Southern Communication Engineering*, vol. 14, no. 54, pp. 17–34, 2025, doi:10.30495/jce.2024.2000184.1235, [in Persian].

### مقاله پژوهشی

طراحی کارآمد تقسیم کننده غیربازیابی برگشتیذیر با قابلیت حفظ توازن

چکىدە

محمد طالبی🕛 | محمد مصلح\*🗗 | محسن چکین🕫

اگروه مهندسی کامپیوتر، واحد دزفول، دانشگاه آزاد اسلامی، دزفول، ایران، Mtalebi@iaud.ac.ir

<sup>۲</sup>گروه مهندسی کامییوتر، واحد دزفول، دانشگاه آزاد اسلامی، دزفول، ایران، Mohammad.Mosleh@iau.ac.ir

<sup>۳</sup> گروه مهندسی کامپیوتر، واحد دزفول، دانشگاه آزاد اسلامی،

یکی از چالشهای اساسی در مدارات مجتمع پرتراکم، اتلاف توان مصرفی است که به واسطه وجود ترانزیستورها در مدارات ایجاد می شود و موجب می گردد دمای مدار افزایش یابد. طراحی مدارات دیجیتال به شیوه برگشتپذیر میتواند به عنوان یکی از رویکردهای کارآمد برای رفع این چالش به کار گرفته شود. علاوه بر این، طراحی مدارات برگشت پذیر با قابلیت حفظ توازن می تواند در تشخیص اشکالات در مدارات بسیار مؤثر باشد. تقسیم کننده ها به عنوان یکی از مدارات پرکاربرد در سیستم های محاسباتی دیجیتال مورد استفاده قرار می گیرند. مدارات تقسیم کننده متشکل از واحدهای پایهای جمع کننده، مالتی پلکسر و دو مدار ترتیبی ثبات و ثبات شیفت به چپ با قابلیت بار شدن موازی هستند. این مقاله یک طراحی جدید و کارآمد از تقسیم کننده غیربازیابی برگشت پذیر با قابلیت حفظ توازن ارائه می کند. برای این منظور در ابتدا یک نگهدارنده حالت نوع D برگشت پذیر با قابلیت حفظ توازن پیشنهاد شده است. سپس یک ثبات n بیتی برگشت پذیر با قابلیت حفظ توازن با استفاده از نگهدارنده حالت برگشت پذیر پیشنهادی ارائه گردیده است. در ادامه یک شیفت ثبات n+1 بیتی برگشت پذیر با قابلیت حفظ توازن با استفاده از نگهدارنده پیشنهادی و سایر دروازههای برگشتپذیر پیشنهاد شده است. در نهایت تقسیم کننده برگشت پذیر n بیتی با قابلیت حفظ توازن بر اساس الگوریتم غیربازیابی توسعه یافته است. نتایج حاصل از مقایسهها نشان میدهند مدار پیشنهادی از لحاظ معيارهاي ارزيابي مدارات برگشت پذير همچون هزينه كوانتومي، تعداد ورودیهای ثابت و تعداد خروجیهای زائد در مقایسه با کارهای پیشین برتری دارند.

كليدواژهها: تقسيم كننده، الگوريتم با روش غيربازيابي، محاسبات كوانتومى، منطقبر گشت پذير، مدار بر گشت پذير با قابليت حفظ توازن

https://doi.org/10.30495/jce.2024.2000184.1235

#### ۱– مقدمه

امروزه یکی از چالشهای مهم در توسعه مدارهای مجتمع پرتراکم مسئله اتلاف توان است که موجب افزایش دمای مدارات شده که این مسئله به عنوان یک نگرانی اساسی در طراحی مدارهای کلاسیک به شمار میرود. از این رو طراحی مدارها در ابعاد نانو از اهمیت ویژهای برخوردار است [۱-۳]. طراحی مدارها با استفاده از منطق بر گشت پذیر ۱ می تواند بر چالش اساسی توان مصرفی فائق آمده و نیز به سبب قابلیت پیادهسازی کوانتومی، پیچیدگی و تراکم مدارها را نیز به میزان قابل توجهی کاهش دهد [۴].

<sup>1</sup> reversible

دزفول، ایران، Chegin@iaud.ac.ir نويسنده مسئول »محمد مصلح، دانشیار، گروه مهندسی کامپیوتر، واحد دزفول، دانشگاه آزاد اسلامی، دزفول، ایران، Mohammad.Mosleh@iaud.ac.ir تاریخ دریافت: ۹ آبان ۱٤۰۲ تاریخ بازنگری: ۱۱ دی ۱٤۰۲ تاریخ پذیرش: ۲۵ دی ۱٤۰۲

بنابراین در آینده نزدیک شاهد بهره گیری گسترده از منطق برگشت پذیر و محاسبات کوانتومی در طراحی مدارهای دیجیتال خواهیم بود [۵, ۶]. علاوه بر این، به منظور طراحی مدارات محاسباتی با قابلیت تحمل پذیری خطا، میتوان از مدارهای برگشت پذیر با قابلیت حفظ توازن استفاده کرد[۷].

لاندور<sup>۲</sup> در سال ۱۹۶۱ ثابت کرد که در محاسبات کلاسیک امروزی، بابت هر بیت از اطلاعات که از بین می رود، به میزان KTLn2 ژول انرژی به صورت انرژی گرمایی آزاد می شود، که K به ثابت بولتزمن و T به دمای مطلق محیط اشاره دارد [۸]. در سال ۱۹۶۵، مور<sup>۳</sup> نظریه اینکه افزایش صددرصدی تعداد ترانزیستورها در حدود هر ۱۸ ماه موجب تولید حرارت و اتلاف انرژی می شود و چالشی با اهمیت در طراحی مدارهای مجتمع خواهد شد را ارائه داد [۹]. در سال ۱۹۷۳، بنت<sup>۴</sup> پیشنهاد داد که استفاده از منطق بر گشت پذیر باعث کاهش توان مصرفی در مدارات خواهد شد [۱۰].

عملیات کوانتومی ذاتاً برگشت پذیر است و دروازههای برگشت پذیر با قابلیت حفظ توازن فاکتورهای با اهمیتی در طراحی مدارهای برگشت پذیر هستند. همچنین ویژگی قابلیت حفظ توازن با استفاده از دروازه هایی که قابلیت حفظ توازن دارند با مقایسه حفظ توازن بین ورودیها و خروجیها به تشخیص خطاهای محاسباتی دائمی و گذرا در مدارهای برگشتیذیر کمک میکند. بنابراین طراحیهای دروازههای برگشتپذیر باقابلیت حفظ توازن از احتمال بروز خطاهای محاسباتی کم میکند [۱۱]. مدارات تقسیم کننده به عنوان یکی از بخشهای اساسی واحدهای محاسباتی دیجیتال محسوب می شوند. تقسیم کنندهها می توانند با استفاده از یکی از رویکردهای بازگردانی<sup>4</sup> و یا غیربازیابی<sup>۶</sup> عملیات تقسیم را انجام دهند [۱۲]، که شامل مجموعهای از عملياتهاي جابجايي، تفريق و جمع هستند. از اين رو مدارات تقسيم كننده از واحدهايي ترتيبي همچون ثبات، شيفت ثبات و نیز واحدهای ترکیبی همچون جمع کننده و مالتی پلکسر تشکیل شده است. در سال ۲۰۰۹، نایم و همکارانش اولین طرح تقسیم کننده یn بیتی برگشت پذیر را برای انجام عملیات تقسیم در بازه اعداد صحیح مثبت با بهره گیری از الگویتم غیربازیابی ارائه نمودند [۱۳]. در طراح ارائه شده مالتی پلکسر n بیتی، ثبات بر گشت پذیر n بیتی و ثبات شیفت به چپ n+1 بیتی بر مبنای گیت FRG و از گیت جمع کننده برگشتیذیر MTSG و گیت TS-3 برای طراحی جمع کننده موازی برگشتیذیر n+1 بیتی استفاده شده است. در تقسیم کننده ارائه شده ورودی های ثابت برابر 11 + 10n، خروجی های زائد برابر 18+11n و هزینه ی كوانتومي برابر 50+61n است. اگرچه تقسیم كننده ارائه شده برگشت پذیر است ولیكن از قابلیت حفظ توازن<sup>۸</sup> برخوردار نیست. در سال ۲۰۱۱، دستان و حق پرست برای اولین بار یک تقسیم کننده n بیتی بر گشت پذیر غیربازیابی با قابلیت حفظ توازن را ارائه نمودند [۱۴]. در این مقاله، دو طراحی متفاوت با استفاده از حافظه نگهدارنده حالت٬ و بدون استفاده از حافظه نگهدارنده حالت ارائه شده است. در ساختار ارائه شده با استفاده از گیتهای FRG و FRG<sup>۱۰</sup> و با پیشنهاد گیتهای متنوع برگشت پذیر، یک مدار جمع کننده n+1 بیتی و یک ثبات شیفت به چپ n+1 بیتی پیشنهاد شده است. طراحی اول شامل 11n+14 ورودی ثابت، 12n+18 خروجی زائد و هزینه یکوانتومی 50+60 است. رویکرد دوم نیز دارای 12n+12 ورودی ثابت، 12n+16 خروجی زائد و هزینه یکوانتومی 53+75n است. در سال ۲۰۱۶، بابو و همکارانش یک تقسیم کننده غیربازیایی برگشتیذیر ممیز شناور n بیتی با قابلیت حفظ توازن ارائه نمودند [۱۵]. در طراحی تقسیم کننده معرفی شده، با ارائه گیتهای برگشت پذیر ۱۱ از پیش طراحی شده و استفاده از گیت DFG یک ثبات شیفت به چپ برگشت پذیر n+1 بیتی، و با ارائه یک تمام جمع کننده تحمل یذیر خطا با عنوان NFTFAG<sup>۱۲</sup> و استفاده از گیت DFG یک جمع کننده موازی n+1 بیتی برگشت یذیر طراحی شده است. تقسیم کننده معرفی شده دارای 17 + 10n ورودی های ثابت، 17 + 12n خروجیهای زائد و هزینهی کوانتومی 69 + 67n است. در سال ۲۰۲۲، طالبی و همکارانش یک تقسیمکننده n بیتی ممیز شناور برگشت پذیر با قابلیت حفظ توازن پیشنهاد نمودند

1 parity-preserving

- <sup>3</sup> Moore <sup>4</sup> Bennett

- <sup>5</sup> restoring

- <sup>6</sup> non-restoring

- 7 Fredkin Gate

- 8 parity-preserving

- <sup>9</sup> Latch

- <sup>10</sup>Double Feynman Gate

- <sup>11</sup> reversible gates

<sup>&</sup>lt;sup>2</sup> Landauer

<sup>&</sup>lt;sup>12</sup> New Fault Tolerant Full Adder Gate

[۱۶]. در این تقسیم کننده طراحیهای کارامدی برای واحدهای سازنده آن شامل جمع کننده، ثبات شیفت به چپ و ثبات n بیتی صورت گرفته است. در این تقسیم کننده با ارائه یک جمع کننده بر گشت پذیر و یک ثبات شیفت به چپ بر اساس گیتهای برگشت پذیر DFG ، FRG و یک نگهدارنده حالت پیشنهادی ارائه گردیده است. مدار پیشنهادی شامل 18 + 18 ورودیهای ثابت، 18 + 15 خروجیهای زائد و هزینهی کوانتومی برابر 68 + 66 است. در این مقاله به ارائه یک تقسیم کننده بر گشت پذیر با قابلیت حفظ توازن بر اساس رویکرد غیربازیابی پرداخته می شود که در آن اصول طراحی بر گشت پذیر به درستی رعایت شده است. ایده ها و نوآوریهای این مقاله به شرح زیر هستند:

- طراحی یک نگهدارنده حالت نوع D<sup>۱</sup> برگشت پذیر تک بیتی کار آمد با قابلیت حفظ توازن

- ارائه یک ثبات n بیتی برگشت پذیر با استفاده از نگهدارنده حالت نوع D پیشنهادی با n ورودی ثابت، n خروجی زائد و هزینه کوانتومی برابر 6n

- پیشنهاد یک ثبات شیفت به چپ با قابلیت بار موازی<sup>۲</sup> برگشت پذیر با قابلیت حفظ توازن با استفاده از هم افزایی حافظه نگهدارنده حالت D پیشنهادی و گیتهای برگشت پذیر FRG و DFG

• توسعه یک تقسیمکننده برگشتپذیر غیربازیابی کارآمد با قابلیت حفظ توازن به کمک مدارات پیشنهاد شده

مقاله به صورت ذیل سازماندهی شده است: در بخش دوم اصول منطق برگشت پذیر و روش تقسیم اعداد به شیوه غیربازیابی پرداخته میشود. در بخش سوم، به توسعه یک تقسیم کننده برگشت پذیر با قابلیت حفظ توازن به کمک تکنیک تقسیم غیربازیابی پرداخته میشود. در بخش چهارم، به ارزیابی و مقایسه طرحهای پیشنهادی با کارهای پیشین می پردازد. در آخر، مقاله با بخش نتیجه گیری خاتمه می یابد.

# ۲-منطق برگشت پذیر و روش تقسیم اعداد

در این بخش در ابتدا به بیان مفاهیم پایهای در منطق برگشتپذیر شامل مفهوم برگشتپذیری، دروازههای برگشتپذیر و نمایشهای کوانتومی دروازههای برگشتپذیر پرداخته میشود. در ادامه به معرفی تقسیم بر اساس الگوریتم غیربازیابی پرداخته خواهد شد.

برخی از معیارهای مهم جهت ارزیابی مدارهای برگشت پذیر به شرح زیر هستند:

تعداد ورودیهای ثابت شامل ورودیهای تنظیم شده مدار برگشتپذیر با مقادیر ثابت صفر و یا یک، تعداد خروجی زائد شامل خروجیهای بلااستفاده هستند و به عنوان ورودی به سایر دروازه های برگشت پذیر استفاده نمیشود. هزینه کوانتومی شامل هزینه کوانتومی یک مدار برگشتپذیر به مجموع دروازههای برگشت پذیر ۲×۲ و دروازههای کنترلی ۷ و †۷، فینمن<sup>۳</sup> (CNOT) و دروازه ۱×۱ وارونگر (NOT) که میتوان هزینه آن را نادیده گرفت، و سایر دروازههای کوانتومی در نظر گرفته میشود [۰۳, ۱۳]. تاخیر عامل مهمی در طراحی مدارهای متوالی است، تعداد انجام مراحل از ورودی به خروجی در یک مدار کوانتومی را عمق مدار گویند و به این ترتیب تاخیر ورودی به خروجی یک مدار کوانتومی متناسب با عمق مدار است [۳۳].

# ۲–۱– دروازههای پایه

– دروازه وارونگر کوانتومی(NOT) :

یک دروازه کوانتومی ۱×۱ با هزینه کوانتومی برابر با یک میباشد که نمایش کوانتومی آن در شکل ۱ نشان داده شده است [۳۱].

<sup>1</sup> D-Latch

<sup>3</sup> Feynman Gate

<sup>&</sup>lt;sup>2</sup> Parallel-In Parallel-Out (PIPO)

$$\mathbf{A} \underbrace{\qquad \qquad} \mathbf{P} = \mathbf{A}^{*}$$

(۳۱] NOT شکل ۱: نمایش کوانتومی دروازه NOT Figure 1: quantum realization of NOT gate [31]

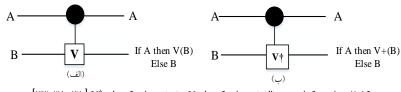

-دروازههای کنترل شونده Vو<sup>†</sup>V :

دروازههای کوانتومی ۲×۲ با هزینه کوانتومی یک و تاخیر V برابر یک و <sup>†</sup>V برابر ∆۲ هستند [۳۲]که نمایش کوانتومی آنها در شکل۲ نشان داده شده است [۳۱, ۳۳–۳۵]. همانطوری که ملاحظه میشود، زمانی که خط کنترل A برابر صفر باشد ورودی بدون تغییر به خروجی منتقل میشود؛ اگر ورودی کنترل A برابر با یک باشد، دروازههای کنترل شونده Controlled-V و †Controlled به ترتیب بصورت خروجیهای (B)V و (B)<sup>†</sup>V به خروجی ارسال میشوند.

شکل ۲: نمایش کوانتومی (الف) دروازه کنترلی ۷ ، (ب) دروازه کنترلی <sup>†</sup>۷ [۳۱, ۳۵–۳۳] Figure 2: quantum realization of (a) Controlled-V gate and (b) Controlled-V<sup>†</sup> gate [31,33-35]

اگر V و <sup>†</sup>V به ترتیب مبین ماتریسهای دروازههای کنترل شونده Controlled-V و <sup>†</sup>Controlled باشند آنگاه روابط زیر برقرار است (۳۶, ۳۷].

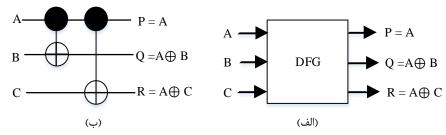

- دروازه برگشتیذیر DFG:

یک دروازه برگشتپذیر ۳×۳ با قابلیت حفظ توازن است که دارای هزینه کوانتومی برابر دو و تاخیر آن برابر ∆۲ است. نمایش کوانتومی در شکل۳ و درستی آن در جدول۱ نمایش داده شده است[۱۹].

شکل ۳: دروازه برگشت پذیر DFG: (الف) بلوک دیا گرام و (ب) مدار کوانتومی [۱۹] Figure 3: reversible DFG gate (a) block diagram and (b) quantum realization [19]

| ل درستی دروازه DFG      | ۱: جدوا | جدول   |

|-------------------------|---------|--------|

| Table 1: truth table of | the DF  | G gate |

|   | خروجى خروجى |   |   |   |   |  |  |  |

|---|-------------|---|---|---|---|--|--|--|

| A | B           | С | Р | 0 | R |  |  |  |

| 0 | 0           | 0 | 0 | Õ | 0 |  |  |  |

| 0 | 0           | 1 | 0 | 0 | 1 |  |  |  |

| 0 | 1           | 0 | 0 | 1 | 0 |  |  |  |

| 0 | 1           | 1 | 0 | 1 | 1 |  |  |  |

| 1 | 0           | 0 | 1 | 1 | 1 |  |  |  |

| 1 | 0           | 1 | 1 | 1 | 0 |  |  |  |

| 1 | 1           | 0 | 1 | 0 | 1 |  |  |  |

| 1 | 1           | 1 | 1 | 0 | 0 |  |  |  |

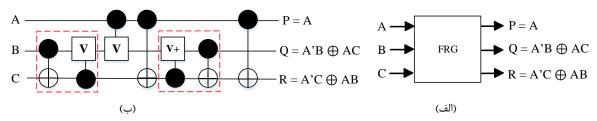

# -دروازه برگشت پذیر FRG:

یک دروازه برگشتپذیر ۳×۳ با قابلیت حفظ توازن است که دارای هزینه کوانتومی برابر پنج و تاخیر برابر △۴ است. نمایش کوانتومی در شکل۴ و درستی آن در جدول۲ نمایش داده شده است [۳۸].

[۳۸] شکل ۴: دروازه برگشت پذیر FRG: (الف) بلوک دیاگرام و (ب) مدار کوانتومی [۳۸] Figure 4: reversible FRG gate (a) block diagram and (b) quantum realization [38]

FRG جدول ۲: جدول درستی دروازه Table 2: truth table of the FRG gate

|   | ورودى |   |   | خروجى |   |  |

|---|-------|---|---|-------|---|--|

| А | В     | С | Р | Q     | R |  |

| 0 | 0     | 0 | 0 | 0     | 0 |  |

| 0 | 0     | 1 | 0 | 0     | 1 |  |

| 0 | 1     | 0 | 0 | 1     | 0 |  |

| 0 | 1     | 1 | 0 | 1     | 1 |  |

| 1 | 0     | 0 | 1 | 0     | 0 |  |

| 1 | 0     | 1 | 1 | 1     | 0 |  |

| 1 | 1     | 0 | 1 | 0     | 1 |  |

| 1 | 1     | 1 | 1 | 1     | 1 |  |

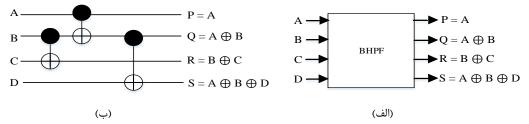

#### - دروازه برگشت یذیر BHPF

یک بلوک برگشتپذیر ۴×۴ با قابلیت حفظ توازن است که هزینه کوانتومی آن برابر سه و تاخیر آن برابر △۳ است. نمایش کوانتومی در شکل ۵ و درستی آن در جدول ۳ نشان داده شده است[۲۴].

شکل۵: دروازه برگشت پذیر BHPF. (الف) بلوک دیاگرام و (ب) مدار کوانتومی [۲۴] Figure 5: reversible BHPF gate (a) block diagram and (b) quantum realization [24]

| وک دیاگرامBHPF    | ں درستی با | ۳: جدول  | جدول |

|-------------------|------------|----------|------|

| Table 2, twith to | blo of the | DIIDE as | ta   |

| ورودى |   |   |   | خروجى |   |   |   |

|-------|---|---|---|-------|---|---|---|

| А     | В | С | D | Р     | Q | R | S |

| 0     | 0 | 0 | 0 | 0     | 0 | 0 | 0 |

| 0     | 0 | 0 | 1 | 0     | 0 | 0 | 1 |

| 0     | 0 | 1 | 0 | 0     | 0 | 1 | 0 |

| 0     | 0 | 1 | 1 | 0     | 0 | 1 | 1 |

| 0     | 1 | 0 | 0 | 0     | 1 | 1 | 1 |

| 0     | 1 | 0 | 1 | 0     | 1 | 1 | 0 |

| 0     | 1 | 1 | 0 | 0     | 1 | 0 | 1 |

| 0     | 1 | 1 | 1 | 0     | 1 | 0 | 0 |

| 1     | 0 | 0 | 0 | 1     | 1 | 0 | 1 |

| 1     | 0 | 0 | 1 | 1     | 1 | 0 | 0 |

| 1     | 0 | 1 | 0 | 1     | 1 | 1 | 1 |

| 1     | 0 | 1 | 1 | 1     | 1 | 1 | 0 |

| 1     | 1 | 0 | 0 | 1     | 0 | 1 | 0 |

| 1     | 1 | 0 | 1 | 1     | 0 | 1 | 1 |

| 1     | 1 | 1 | 0 | 1     | 0 | 0 | 0 |

| 1     | 1 | 1 | 1 | 1     | 0 | 0 | 1 |

<sup>&</sup>lt;sup>1</sup> Bolhassani Haghparast Parity-Preserving Full-adder (BHPF)

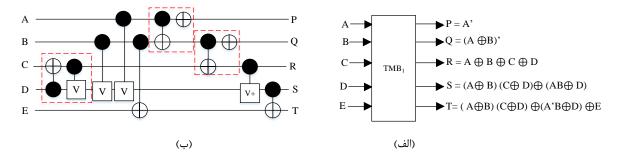

### - بلوک برگشت پذیر TMB1<sup>·</sup>:

یک بلوک برگشتپذیر ۵×۵ با قابلیت حفظ توازن است که هزینه کوانتومی برابر با هشت و تاخیر △۶ برخوردار است؛ نمایش کوانتومی بلوک TMB1 در شکل ۶ و درستی آن در جدول ۴ نشان داده شده است[۱۶].

(۱۶) شکل ۶۰ بلوک منطقی برگشت پذیر TMB1: (الف) بلوک دیاگرام و (ب) مدار کوانتومی [۱۶] Figure 6: reversible TMB1 logical block: (a) block diagram and (b) quantum realization [16]

|   | Table 4: truth table of the TMB1 block |   |   |   |   |   |    |     |   |

|---|----------------------------------------|---|---|---|---|---|----|-----|---|

|   | ورودى                                  |   |   |   |   |   | جى | خرو |   |

| А | В                                      | С | D | Е | Р | Q | R  | S   | Т |

| 0 | 0                                      | 0 | 0 | 0 | 1 | 1 | 0  | 0   | 0 |

| 0 | 0                                      | 0 | 0 | 1 | 1 | 1 | 0  | 0   | 1 |

| 0 | 0                                      | 0 | 1 | 0 | 1 | 1 | 1  | 1   | 1 |

| 0 | 0                                      | 0 | 1 | 1 | 1 | 1 | 1  | 1   | 0 |

| 0 | 0                                      | 1 | 0 | 0 | 1 | 1 | 1  | 0   | 0 |

| 0 | 0                                      | 1 | 0 | 1 | 1 | 1 | 1  | 0   | 1 |

| 0 | 0                                      | 1 | 1 | 0 | 1 | 1 | 0  | 1   | 1 |

| 0 | 0                                      | 1 | 1 | 1 | 1 | 1 | 0  | 1   | 0 |

| 0 | 1                                      | 0 | 0 | 0 | 1 | 0 | 1  | 0   | 1 |

| 0 | 1                                      | 0 | 0 | 1 | 1 | 0 | 1  | 0   | 0 |

| 0 | 1                                      | 0 | 1 | 0 | 1 | 0 | 0  | 0   | 1 |

| 0 | 1                                      | 0 | 1 | 1 | 1 | 0 | 0  | 0   | 0 |

| 0 | 1                                      | 1 | 0 | 0 | 1 | 0 | 0  | 1   | 0 |

| 0 | 1                                      | 1 | 0 | 1 | 1 | 0 | 0  | 1   | 1 |

| 0 | 1                                      | 1 | 1 | 0 | 1 | 0 | 1  | 1   | 0 |

| 0 | 1                                      | 1 | 1 | 1 | 1 | 0 | 1  | 1   | 1 |

| 1 | 0                                      | 0 | 0 | 0 | 0 | 0 | 1  | 0   | 0 |

| 1 | 0                                      | 0 | 0 | 1 | 0 | 0 | 1  | 0   | 1 |

| 1 | 0                                      | 0 | 1 | 0 | 0 | 0 | 0  | 0   | 0 |

| 1 | 0                                      | 0 | 1 | 1 | 0 | 0 | 0  | 0   | 1 |

| 1 | 0                                      | 1 | 0 | 0 | 0 | 0 | 0  | 1   | 1 |

| 1 | 0                                      | 1 | 0 | 1 | 0 | 0 | 0  | 1   | 0 |

| 1 | 0                                      | 1 | 1 | 0 | 0 | 0 | 1  | 1   | 1 |

| 1 | 0                                      | 1 | 1 | 1 | 0 | 0 | 1  | 1   | 0 |

| 1 | 1                                      | 0 | 0 | 0 | 0 | 1 | 0  | 1   | 0 |

| 1 | 1                                      | 0 | 0 | 1 | 0 | 1 | 0  | 1   | 1 |

| 1 | 1                                      | 0 | 1 | 0 | 0 | 1 | 1  | 0   | 1 |

| 1 | 1                                      | 0 | 1 | 1 | 0 | 1 | 1  | 0   | 0 |

| 1 | 1                                      | 1 | 0 | 0 | 0 | 1 | 1  | 1   | 0 |

| 1 | 1                                      | 1 | 0 | 1 | 0 | 1 | 1  | 1   | 1 |

| 1 | 1                                      | 1 | 1 | 0 | 0 | 1 | 0  | 0   | 1 |

| 1 | 1                                      | 1 | 1 | 1 | 0 | 1 | 0  | 0   | 0 |

جدول۴: جدول درستی بلوک TMB1 Table 4: truth table of the TMB1 bloc

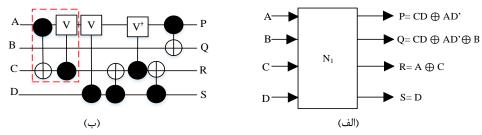

# -بلوک منطقی برگشت پذیر N1 :

یک بلوک برگشتپذیر ۴×۴ با قابلیت حفظ توازن است که دارای هزینه کوانتومی برابر با شش و تاخیر △۵ بوده و نمایش کوانتومی در شکل ۷ و درستی آن در جدول ۵ نشان داده شده است[۳۹].

<sup>&</sup>lt;sup>1</sup> Talebi Mosleh Block1 (TMB1)

| جدول ۵: جدول درستی بلوک N1           |

|--------------------------------------|

| Table 5: truth table of the N1 block |

| ورودى |   |   |   | خروجى |   |   |   |  |

|-------|---|---|---|-------|---|---|---|--|

| А     | В | С | D | Р     | Q | R | S |  |

| 0     | 0 | 0 | 0 | 0     | 0 | 0 | 0 |  |

| 0     | 0 | 0 | 1 | 0     | 0 | 0 | 1 |  |

| 0     | 0 | 1 | 0 | 0     | 0 | 1 | 0 |  |

| 0     | 0 | 1 | 1 | 1     | 1 | 1 | 1 |  |

| 0     | 1 | 0 | 0 | 0     | 1 | 0 | 0 |  |

| 0     | 1 | 0 | 1 | 0     | 1 | 0 | 1 |  |

| 0     | 1 | 1 | 0 | 0     | 1 | 1 | 0 |  |

| 0     | 1 | 1 | 1 | 1     | 0 | 1 | 1 |  |

| 1     | 0 | 0 | 0 | 1     | 1 | 1 | 0 |  |

| 1     | 0 | 0 | 1 | 0     | 0 | 1 | 1 |  |

| 1     | 0 | 1 | 0 | 1     | 1 | 0 | 0 |  |

| 1     | 0 | 1 | 1 | 1     | 1 | 0 | 1 |  |

| 1     | 1 | 0 | 0 | 1     | 0 | 1 | 0 |  |

| 1     | 1 | 0 | 1 | 0     | 1 | 1 | 1 |  |

| 1     | 1 | 1 | 0 | 1     | 0 | 0 | 0 |  |

| 1     | 1 | 1 | 1 | 1     | 0 | 0 | 1 |  |

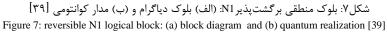

# ۲-۲-الگوريتم تقسيم كننده غيربازيابي

عمل تقسیم به عنوان یکی از عملیاتهای مهم و با پیچیدگی بالا در سیستمهای محاسباتی محسوب میشود. یکی از متداول ترین الگوریتمهای تقسیم، الگوریتم غیربازیابی است [۱۳]. روش کار در این الگوریتم به اینصورت است که پس از عملیات شیفت به چپ عملیات بازگردانی را میتوان از طریق معادله K<sub>i+1</sub>=2R<sub>i</sub>+V پیادهسازی نمود. در این تکنیک اگر نتیجه معادله منفی شد، باقیمانده جزئی سریعاً ذخیره نخواهد شد و عملیات جمع، تفریق و بازیابی به وسیله معادلات V و R<sub>i</sub>=R<sub>i</sub>+R و میادله معادله R<sub>i+1</sub>=2R<sub>i</sub>+V پیادهسازی نمود. در این تکنیک اگر نتیجه معادله منفی شد، باقیمانده جزئی سریعاً ذخیره نخواهد شد و عملیات جمع، تفریق و بازیابی به وسیله معادلات V و R<sub>i=</sub>R<sub>i</sub>=R<sub>i</sub>+V میشود. بازیابی به وسیله معادلات V و R<sub>i+1</sub>=2R<sub>i</sub>+V و معادله منفی شد، باقیمانده جزئی سریعاً ذخیره نخواهد شد و عملیات جمع، تفریق و بازیابی به وسیله معادلات V و R<sub>i</sub>=R<sub>i</sub>=R<sub>i</sub>+V و میشود. بازیابی به وسیله معادلات V<sub>i</sub>=R<sub>i</sub>-R<sub>i</sub>-V و معادله می تفریق و بازیابی به وسیله معادلات V<sub>i</sub>=R<sub>i</sub>-R<sub>i</sub>-V و R<sub>i</sub>-R<sub>i</sub>-V و میشود. بازیابی به وسیله معادلات V<sub>i</sub>=R<sub>i</sub>-R<sub>i</sub>-V و R<sub>i</sub>-Y و R<sub>i</sub>-Y و میشود. بازیابی اگر خارج قسمت I و R<sub>i</sub>=R<sub>i</sub>-V و میستم معاد می تفریق حساب میشود و اگر خارج قسمت O a state می معاد می تفریق حساب میشود و اگر از (۸) و R<sub>i</sub>-C

# ۳- تقسیم کننده برگشت پذیر پیشنهادی

در این بخش به تشریح فرآیند طراحی تقسیم کننده پیشنهادی پرداخته خواهد شد. برای این منظور در ابتدا واحدهای تشکیل دهنده تقسیم کننده پیشنهادی طراحی می شوند و سپس با استفاده از اجزا طراحی شده به توسعه تقسیم کننده غیربازیابی بر گشت پذیر با قابلیت حفظ توازن پرداخته می شود.

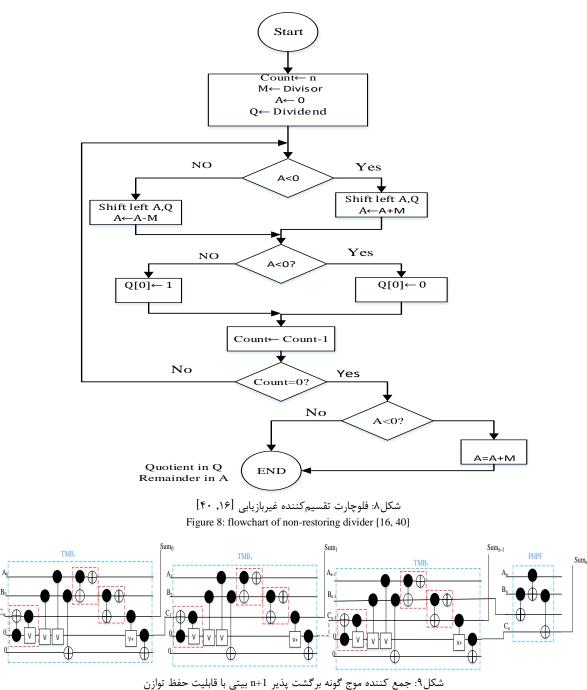

## **--- جمع کننده موج گونه برگشت پذیر با قابلیت حفظ توازن**

در تقسیم کننده پیشنهادی از جمع کننده موج گونه n+1 بیتی برگشت پذیر کارامد با قابلیت حفظ توازن که در مرجع [18] ارائه گردیده استفاده می شود که نمایش کوانتومی آن در شکل ۹ نشان داده شده است.

حل؟ : جمع كننده موج كونه بر كشت پدير ١٩+١ بيني با قابليك خفط توارن Figure 9: parity-preserving reversible (n+1)-bit RCA adder

# ۲-۳- مالتی پلکسر برگشت پذیر با قابلیت حفظ توازن

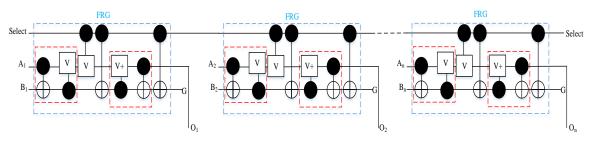

یک مالتی پلکسر n بیتی برگشتپذیر با استفاده از پشت سرهم قراردادن n دروازه FRG همانند شکل ۱۰ طراحی می شود. خطوط (A1, A2,..., An) A و (B1, B2,..., B3) B ورودی های مالتی پلکسر و Select ورودی انتخاب آن می باشد که اگر برابر صفر باشد، خروجی مالتی پلکسر برابر A و اگر برابر یک باشد، خروجی مالتی پلکسر برابر B است. مالتی پلکسر برگشت پذیر معرفی شده فاقد ورودی ثابت، n خروجی زائد و هزینه کوانتومی برابر 5n و با فرض n برابر با یک تاخیر آن برای یک بیت مالتی پلکسر برابر △۴ است [۱۳].

شکل ۱۰: نمایش کوانتومی مالتی پلکسر برگشت پذیر n بیتی با قابلیت حفظ توازن Figure 10: quantum realization of parity-preserving reversible n-bit multiplexer

۳-۳-ثبات برگشت یذیر پیشنهادی با قابلیت حفظ توازن

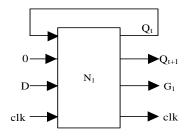

یکی از اجزا اساسی در مدارات تقسیم کننده، وجود عناصر حافظه است. برای این منظور یک نگهدارنده حالت نوع D<sup>۸</sup> کارامد با استفاده از بلوک NI معرفی شده در مرجع[۳۹] طراحی میشود. بلوک برگشت پذیر نگهدارنده حالت نوع D پیشنهادی بر اساس بلوک برگشت پذیر N1 در شکل ۱۱ نشان داده شده است؛ و همانطوری که در شکل مشاهده میشود، اگر خروجی P بلوک IN به ورودی A وصل شود و مقدار ورودی B برابر با مقدار صفر شود؛ همچنین ورودی C به مقدار D ، و ورودی/خروجی D به Clk تنظیم گردند، طبق رابطه ۴ و بر اساس خروجی Q بلوک فوق یک نگهدارنده حالت از نوع D بدست خواهد آمد. نگهدارنده حالت پیشنهادی دارای یک ورودی ثابت، یک خروجی زائد و هزینه کوانتومی برابر شش و تاخیر آن برابر △۵ است.

$$Q_{t+1} = D.CLK + \overline{CLK}.Q_t$$

شکل ۱۱: بلوک برگشت پذیر نگهدارنده حالت نوع D پیشنهادی Figure 11: reversible block of proposed D-latch

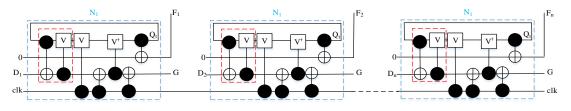

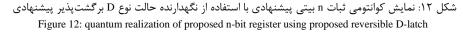

همانطوری که در شکل ۱۲ نشان داده شده است، ثبات n بیتی پیشنهادی با استفاده از پشت سرهم قرار دادن n بلوک نگهدارنده حالت پیشنهادی طراحی شده است. ثبات پیشنهادی دارای n ورودی ثابت، n خروجی زائد و هزینه کوانتومی برابر 6n و تاخیر آن با فرض n مساوی با یک، برای یک بیت رجیستر برابر ۵۵ است.

(۴)

۳-۴-ثبات شیفت به چپ با قابلیت بار موازی برگشت پذیر پیشنهادی با قابلیت حفظ توازن ثبات شیفت به چپ با قابلیت بار موازی برای ذخیرهسازی موقت و همچنین تاخیر زمانی دادهها در مدار تقسیم کننده استفاده شده است. عملکرد آن به این صورت است که همه بیتها با لبه اولین کلاک به صورت موازی در ثبات بارگذاری خواهند شد و بعد از عملیات شیفت همه بیتها یکباره به خروجی ارسال می گردند. ورودیهای کنترلی SV و E بر اساس رابطه ۵ عملکرد خروجی ثبات را با توجه به مقادیر ورودی توابع کنترلی در جدول ۶ نشان میدهند [۱۳].

$$Q_i = SV'.E.I_i + SV'.E'.Q_{i-1} + SV.Q_i$$

| نپ   | های ثبات شیفت به چ     | ۶: توابع کنترلی ورودی        | جدوا         |

|------|------------------------|------------------------------|--------------|

| Tab  | le 6: Control function | ns of left-shift register i  | nputs        |

| Mode | control                | Output <b>Q</b> <sub>i</sub> | عمليات       |

| Ε    | SV                     | _                            | - <b>.</b> - |

| 0    | 0                      | $Q_{i-1}$                    | شيفت به چپ   |

| 1    | 0                      | $I_i$                        | بار موازی    |

| ×    | 1                      | $Q_i$                        | بدون تغيير   |

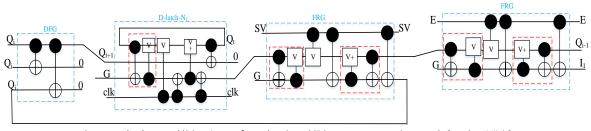

در ادامه ثبات شیفت به چپ برگشت پذیر با قابلیت بار شدن موازی و توانایی حفظ توازن با استفاده از نگهدارنده حالت نوع D پیشنهادی، دو دروازه FRG و یک دروازه DFG مطابق شکل ۱۳ طراحی شده است. مدار پیشنهادی دارای سه ورودی ثابت، سه خروجی زائد و هزینه کوانتومی برابر ۱۸ و تاخیر آن با فرض n مساوی با یک، برای یک بیت رجیستر شیفت به چپ برابر ۱۵۵

شکل۱۳: نمایش کوانتومی ثبات شیفت به چپ با قابلیت بار موازی برگشت پذیر با قابلیت حفظ توازن پیشنهادی Figure 13: quantum realization of proposed parity-preserving reversible PIPO left-shift register

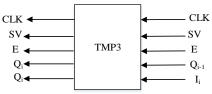

به منظور بکارگیری مدار معرفیشده در طراحی یک سلول ثبات شیفت به چپ n بیتی، مدار ثبات شیفت پیشنهادی به صورت یک بلوک ۵×۵ با نام TMP3 در شکل ۱۴ نشان داده شده است.

شکل ۱۴: سلول تک بیتی ثبات شیفت به چپ با قابلیت بار موازی بر گشت پذیر پیشنهادی با قابلیت حفظ توازن Figure 14: one-bit cell of proposed parity-preserving reversible PIPO left-shift register

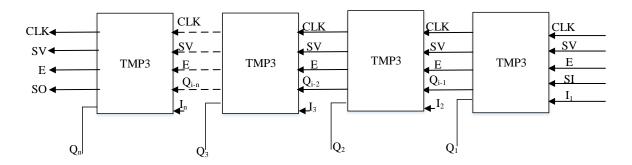

به منظور طراحی یک ثبات شیفت به چپ n+1 بیتی برگشت پذیر با قابلیت بار موازی و توانایی حفظ توازن، n بلوک پیشنهادی TMP3 به صورت آبشاری به یکدیگر متصل میشوند (مطابق شکل ۱۵). لازم به ذکر است مدار پیشنهادی داری 3n ورودی ثابت، 5+3n خروجی زائد و هزینه کوانتومی برابر 18+18 است.

(۵)

شکل۱۵: ثبات n+1 بیتی شیفت به چپ برگشت پذیر پیشنهادی با قابلیت بار موازی و توانایی حفظ توازن Figure 15: proposed parity-preserving reversible PIPO left-shift (n+1)-bit register

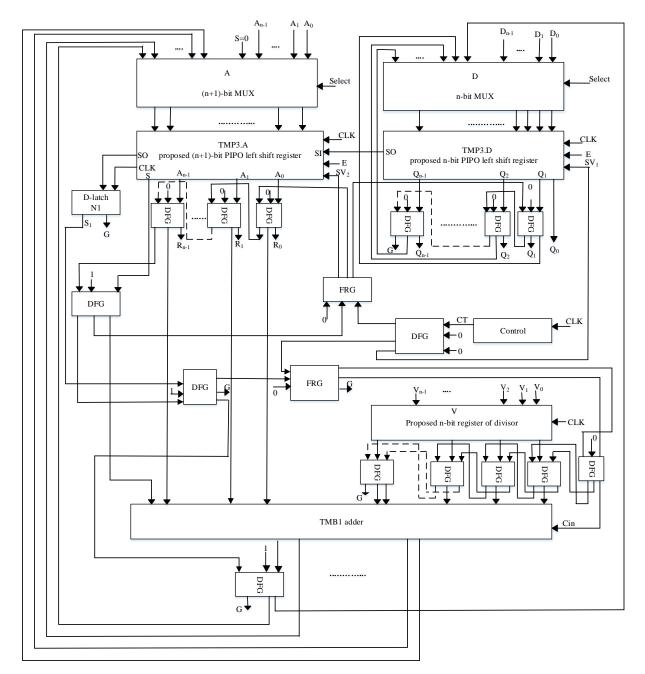

#### ۵-۳ تقسیم کننده پیشنهادی

در این بخش به ارائه یک طراحی بهینه از مدار تقسیم کننده غیربازیابی برگشت پذیرn بیتی برگشت پذیر با قابلیت حفظ توازن برای تقسیم اعداد صحیح مثبت مبتنی بر معماری معرفی شده در [۱۴,۱۳] پرداخته می شود. معماری تقسیم کننده بر گشت پذیر بر اساس طراحی پیشنهادی در شکل۱۶، شامل دو مالتی پلکسر n بیتی با نام D و مالتی پلکسر n+1 بیتی با نام A، ثبات شیفت به چپ با قابلیت بار موازی n بیتی باعنوان TMP3.A و ثبات شیفت n+1 بیتی با عنوان TMP3.D نام گذاری شدهاند. یک ثبات n بیتی با عنوان V جهت ذخیره مقسوم علیه، یک نگهدارنده حالت D با عنوان N1 به منظور نگهداری S1 (S1 مقدار سرریزی که از سمت ثبات شیفت TMP3.A در نگهدارنده حالت N1 نگهداری می شود) و یک جمع کننده موج گونه n+1 بیتی می باشد. مقادیر اولیه مالتی پلکسرهای A برابر A است. مقسوم<sup>۱</sup> مقسوم<sup>۱</sup> (A<sub>n-1</sub> A<sub>n-2</sub>....A) و S=0 (ورودی S وصل است به مالتی پلکسر A) است. مقسوم<sup>۱</sup> برابر با مقسوم عليه  $^{7}$ برابر با  $V(V_{n-1}V_{n-2}...V_{0})$  وكنترل برابر با صفر است. ثباتهاى شيفت به چپ به ترتيب  $O(D_{n-1}D_{n-2}...D_{0})$ عبار تند از: خارج قسمت<sup>۳</sup> تقسیم کننده برابر با TMP3.D (Q<sub>n-1</sub>Q<sub>n-2</sub>...Q<sub>0</sub>) و باقیمانده<sup>۴</sup> برابر با TMP3.A (A<sub>n-1</sub>A<sub>n-2</sub>...A<sub>0</sub>) هستند. وقتی یالس ساعت اعمال شود: اگر SV2=0 و E=1 باشد، ورودی S=1 می شود و خروجی از مالتی پلکسر n+1 بیتی A بصورت موازی در ثبات TMP3.A جایگذاری می شود. اگر E=1 و SV1=0 باشد، خروجی از مالتی یلکسر n بیتی در ثبات TMP3.D به صورت موازی جایگذاری می شود. اگر E=0 باشد هر دو ثبات شیفت به چپ عملیات شیفت را انجام می دهند. خروجی SO از ثبات شيفت به چپ n بيتي TMP3.D به SI از ثبات شيفت به چپ n+1 بيتي TMP3.A وصل است. همچنين SO از خروجي ثبات TMP3.A به نگهدارنده حالت N1 وصل است. اگر واحد کنترل select=1 شود E=0 خواهد شد، و عملیات شیفت از خروجی SO از ثبات n بیتی TMP3.D به SI از ثبات n+1 بیتی TMP3.A انجام خواهد شد. پس از عملیات شیفت مقدار SO از ثبات TMP3.A به نگهدارنده حالت N1 منتقل می شود و عملیات جمع کننده را تعیین می کند. خروجی نگهدارنده حالت N1 مکمل می شود، اگر خروجی نگهدارنده حالت برابر با 1 باشد سیس عملیات TMP3.D + V محاسبه می شود در غیر اینصورت اگر صفر باشد عمليات TMP3.D - V محاسبه خواهد شد و نتيجهی عمليات جمع يا تفريق به جمع کننده n+1 بيتی ارسال می شود. در این روش بعد از 1+12 کلاک پالس فرآیند تقسیم پایان مییابد، اگر سیگنال خروجی بلوک کنترل در مدار به 1 تغییر یابد در این شرایط اگر S=0 باشد؛ SV2=1 خواهد بود و TMP3.A باقیمانده جزئی را ذخیره می کند؛ اما اگر S=1 باشد بعد از 1+1 کلاک پالس باقیمانده جزئی باید به وسیله جمع باقیمانده جزئی و خارج قسمت (جمع V با TMP3.D) بازگردانی شود. سپس با کلاک بعدی وقتی select=0 باشد، متمم پر ارزشترین بیت (MSB) حاصل از محاسبه جمع کننده در بیت Q<sub>0</sub> ثبات TMP3.D جایگذاری می شود و با کلاک بعدی حاصل محاسبه جمع کننده به کم ارزشترین بیت (LSB) از ثبات TMP3.A شیفت پیدا می کند. در طراحی، از بلوک DFG برای کپی کردن سیگنال CT به دروازه FRG استفاده شده است. دروازه FRG می تواند عملگر AND را پیادهسازی کند و دو خروجی یکسان تولید کند که یکی از خروجیها به ورودی SV2 و دیگری به جمع کننده متصل

<sup>1</sup> dividend

<sup>&</sup>lt;sup>2</sup> divisor

<sup>&</sup>lt;sup>3</sup> quotient <sup>4</sup> remainder

شده است. زمانیکه TMP3.D مقدار خارج قسمت را ذخیره می کند و پس از باز گردانی باقیمانده، S باید برابر صفر باشد. در شکل ۱۶، مدار تقسیم کننده n بیتی برگشتپذیر پیشنهادی با قابلیت حفظ توازن نشان داده شده است. در طراحی ساختار تقسیم کننده پیشنهادی از ترکیب اجزای پیشنهادشده، استفاده شده است.

شکل ۱۶: مدار تقسیم کننده غیربازیابی n بیتی برگشت پذیر پیشنهادی با قابلیت حفظ توازن Figure 16: proposed parity-preserving reversible n-bit non-restoring divider circuit

#### ۴-مقایسه و ارزیابی

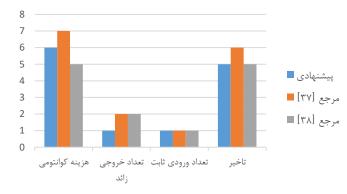

در این بخش به بررسی ارزیابی کارایی طرحهای پیشنهادی از دیدگاه معیارهای ارزیابی مدارات برگشت پذیر شامل ورودی ثابت، خروجی زائد و هزینه کوانتومی پرداخته میشود. معیارهای استفاده شده بصورت مستقل از فناوری ساخت هستند. ثبات برگشت پذیر پیشنهادی با دو ثبات برگشت پذیر ارائه شده در مراجع [۴۱, ۴۲] مورد بررسی و مقایسه قرار گرفته است که نتایج حاصله در جدول ۷ و با فرض n=1 در نمودار شکل ۱۷ نشان داده شده است.

| قابليت حفظ | تاخير با      | تعداد ورودى ثابت | تعداد خروجي | هزينه    | طراحى                  |

|------------|---------------|------------------|-------------|----------|------------------------|

| توازن      | فرضn=1        |                  | زائد        | كوانتومى |                        |

| دارد       | $5 \triangle$ | n                | n           | бn       | پیشنهادی               |

| دارد       | $6 \triangle$ | n                | n+1         | 7n       | ارائه شده در مرجع [41] |

| ندارد      | $5 \triangle$ | n                | n+1         | 5n       | ارائه شده در مرجع [42] |

جدول۲: مقایسه ثبات برگشت پذیر پیشنهادی با کارهای پیشین

شکل ۱۷: نمودار مقایسه ثبات برگشت پذیر Figure 17: comparison chart of reversible register

همان طور که در جدول ۲ ملاحظه می گردد، ثبات بر گشت پذیر پیشنهادی در مقایسه با مرجع [۴۱] از لحاظ کمتر شدن پارامترهای هزینه کوانتومی، خروجی زائد و تاخیر و در مقایسه برتری دارد و در مقایسه با مرجع [۴۲] از لحاظ کمتر بودن پارامترهای خروجی زائد و داشتن قابلیت حفظ توازن برتری دارد.

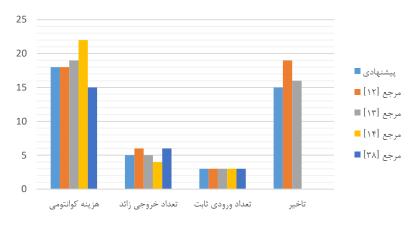

ثبات شیفت به چپ n+1 بیتی با قابلیت بار موازی برگشت پذیر پیشنهادی با چهار طرح موجود در مراجع[۱۳–۱۵, ۴۲] مورد ارزیابی و مقایسه قرار گرفته است که نتایج آن در جدول ۸ و با فرض n=1 در نمودار شکل ۱۸ نشان داده شده است.

| قابليت حفظ | تاخير با       | تعداد ورودي | تعداد خروجى | هزينه    | طراحى               |

|------------|----------------|-------------|-------------|----------|---------------------|

| توازن      | فرضn=1         | ثابت        | زائد        | كوانتومى |                     |

| دارد       | 15△            | 3n          | 3n + 2      | 18n      | پیشنهادی            |

| ندارد      | 19△            | 3n          | 3n + 3      | 18n      | ئه شده در مرجع [13] |

| دارد       | $16 \triangle$ | 3n          | 3n + 2      | 19n      | ئه شده در مرجع [14] |

| دارد       | -              | 3n          | 3n + 1      | 22n      | ئه شده در مرجع [15] |

| ندار د     | 14△            | 3n          | 3n + 3      | 15n      | ئه شده در مرجع [42] |

جدول۸: مقایسه ثبات شیفت به چپ با قابلیت بار موازی برگشت پذیر پیشنهادی با کارهای پیشین Table 8: comparison of proposed reversible PIPO left-shift register with previous works

همان طور که در جدول ۸ ملاحظه می شود، ثبات شیفت پیشنهادی در مقایسه با طرح ارائه شده در مرجع [۱۳] از نظر تعداد خروجی های زائد و تاخیر، در مقایسه با طرح ارائه شده در مرجع [۱۴] از لحاظ هزینه کوانتومی و تاخیر، در مقایسه با طرح ارائه شده در مرجع [۱۵] از لحاظ هزینه کوانتومی، و نهایتاً در مقایسه با طرح ارائه شده در مرجع [۴۲] از لحاظ کمتر شدن خروجی زائد و داشتن قابلیت حفظ توازن برتری دارد.

در نهایت به مقایسه تقسیم کننده n بیتی بر گشت پذیر پیشنهادی با طرحهای ارائه شده در مراجع [۱۴–۱۶] پرداخته می شود. با توجه به پیچیدگی بالای مدارا تقسیم کننده، در ابتدا یک ارزیابی دقیق از اجزا تشکیل دهنده تقسیم کننده پیشنهادی در جدول ۹ ارائه شده است.

شکل ۱۸: نمودار مقایسه ثبات شیفت به چپ با قابلیت بار موازی برگشت پذیر Figure 18: comparison chart of reversible PIPO left-shift register

| قابليت    | تاخير با                      | تعداد ورودى | تعداد      | هزينه    | طرح                           |

|-----------|-------------------------------|-------------|------------|----------|-------------------------------|

| حفظ توازن | فرضn=1                        | ثابت        | خروجي زائد | كوانتومى |                               |

| دارد      | $4\triangle$                  | 0           | n          | 5n       | مالتی پلکسر n بیتی            |

| دارد      | 4∆+4∆                         | 0           | n+1        | 5n+5     | مالتی پلکسر (n+1) بیتی        |

| دارد      | $5 \triangle$                 | n           | n          | 6n       | ثبات n بیتی                   |

| دارد      | 15△                           | 3n          | 3n+2       | 18n      | ثبات شیفت به <i>چپ</i> n بیتی |

| دارد      | $15 \triangle + 15 \triangle$ | 3n          | 3n+5       | 18n+18   | ثبات شیفت به چپ (n+1) بیتی    |

| دارد      | $9 \triangle$                 | n+4         | 3n+2       | 8n+3     | جمع کنندہ (n+1) بیتی          |

| دارد      | $27 \triangle$                | 2n+8        | 6          | 6n+24    | ساير دروازه ها/بلوک           |

| پیشنهادی با قابلیت حفظ توازن   | تقسيم كننده برگشتپذير    | جدول۹: نتایج حاصل از ارزیابی |

|--------------------------------|--------------------------|------------------------------|

| Table 9: results of evaluation | on of proposed parity-pr | eserving reversible divider  |

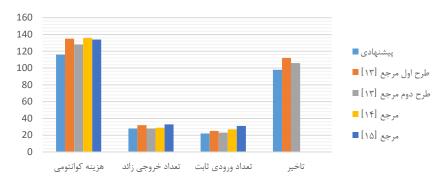

طبق محاسبات جدول ۹ تقسیم کننده n بیتی پیشنهادی دارای هزینه کوانتومی برابر 50+660، خروجی زائد برابر 16+12۱، ورودی ثابت برابر 10+12 و تاخیر برابر △98 میباشد. نتایج حاصل از مقایسه تقسیم کننده پیشنهادی با طراحیهای ارائه شده در مراجع [۱۴-۱۶] در جدول ۱۰ و با فرض n=1 در نمودار شکل ۱۹ نشان داده شده است.

| Table 9: comparison results of proposed reversible divider with previous works |                 |          |            |                |                       |

|--------------------------------------------------------------------------------|-----------------|----------|------------|----------------|-----------------------|

| قابليت حفظ توازن                                                               | تاخير با        | ورودى    | خروجي زائد | هزينه كوانتومي | طرح                   |

|                                                                                | فرضn=1          | ثابت     |            |                |                       |

| دارد                                                                           | 98△             | 10n+12   | 12n+16     | 66n + 50       | طرح پیشنهادی          |

| دارد                                                                           | 112△            | 11n + 14 | 12n + 20   | 75n + 60       | طرح اول موجود در [۱۴] |

| دارد                                                                           | $106 \triangle$ | 11n+12   | 12n+16     | 75n + 53       | طرح دوم موجود در [۱۴] |

| دارد                                                                           | -               | 10n+17   | 12n+17     | 67n + 69       | طرح موجود در [۱۵]     |

| دارد                                                                           | 110△            | 13n+18   | 15n+18     | 66n + 68       | طرح موجود در [۱۶]     |

جدول ۱۰: نتایج مقایسه تقسیم کننده بر گشت پذیر پیشنهادی با کارهای پیشین ble 9: comparison results of proposed reversible divider with previous work

همان طور که در جدول ۱۰ ملاحظه می شود، تقسیم کننده پیشنهادی در مقایسه با طرح اول ارائه شده در مرجع [۱۴] از لحاظ هزینه کوانتومی، خروجی زائد، ورودی ثابت و تاخیر، و در مقایسه با طرح دوم ارائه شده در مرجع [۱۴] نیز از لحاظ هزینه کوانتومی، ورودی ثابت و تاخیر بهبود داده شده است. در مقایسه با طرح ارائه شده در مرجع [۱۵] از لحاظ هزینه کوانتومی، خروجی زائد و ورودی ثابت، و در مقایسه با طرح ارائه شده در مرجع [۱۶] از لحاظ هزینه کوانتومی، ثابت و تاخیر بهینه شده است. نتایج حاصل نشان می دهد طرح پیشنهادی نسبت به طرحهای موجود پارامترهای ارزیابی بهینه و هزینه کوانتومی کمتری دارد.

شکل ۱۹: نمودار مقایسه تقسیم کننده بر گشت پذیر Figure 19: comparison chart of reversible divider

### ۵- نتیجه گیری و پیشنهادات آتی

در این مقاله یک طراحی بهینه از مدار تقسیم کننده بر گشت پذیر غیربازیابی n بیتی با قابلیت حفظ توازن برای تقسیم اعداد صحیح مثبت پیشنهاد شد. برای این منظور، در ابتدا یک حافظه نگهدارنده حالت نوع D برگشت پذیر با قابلیت حفظ توازن پیشنهاد شده است، سپس با استفاده از نگهدارنده حالت پیشنهادی، یک ثبات برگشت پذیر کارامد ارائه گردید. در ادامه یک ثبات شیفت به کمک همافزایی گیتهای برگشت پذیر FRG و DFG و نگهدارنده حالت نوع D پیشنهادی ارائه شد. در نهایت با کمک مدارات برگشت پذیر پیشنهادی، یک تقسیم کننده غیربازیابی برگشت پذیر بهینه توسعه یافت. همچنین به منظور کاهش پیچیدگی تقسیم کننده پیشنهادی، از بهترین مدارات جمع کننده و مالتی پلکسرهای برگشت پذیر موجود استفاده گردید. نتایج حاصل از ارزیابیها نشان می دهد تقسیم کننده پیشنهادی دارای 12+10 ورودی ثابت، 10+20 خروجی زائد، و هزینه کوانتومی حاصل از ارزیابیها نشان می دهد تقسیم کننده پیشنهادی دارای 12+10 ورودی ثابت، 10+20 خروجی زائد، و هزینه کوانتومی ماصل از ارزیابیها نشان می دهد تقسیم کننده پیشنهادی دارای 12+10 ورودی ثابت، 10+20 خروجی زائد، و هزینه کوانتومی طراحی پیشین است. برای کارهای آتی، پیادهسازی تقسیم کننده غیربازیابی پیشنهادی با استفاده از توماتای سلولی نقطه

#### مراجع:

- S. R. Heikalabad, F. Salimzadeh and Y. Z. Barughi, "A unique three-layer full adder in quantum-dot cellular automata," *Computers & Electrical Engineering*, vol. 86, p. 106735, 2020, doi: 10.1016/j.compeleceng.2020.106735.

- [2] S.-S. Ahmadpour, M. Mosleh and S. R. Heikalabad, "An efficient fault-tolerant arithmetic logic unit using a novel fault-tolerant 5-input majority gate in quantum-dot cellular automata," *Computers & Electrical Engineering*, vol. 82, p. 106548, 2020, doi: 10.1016/j.compeleceng.2020.106548.

- [3] R. Binaei and M. Gholami, "Design of novel D flip-flops with set and reset abilities in quantum-dot cellular automata nanotechnology," *Computers & Electrical Engineering*, vol. 74, pp. 259-272, 2019, doi: 10.1016/j.compeleceng.2019.02.002.

- [4] M. Noorallahzadeh, M. Mosleh and S.-S. Ahmadpour, "Efficient designs of reversible synchronous counters in nanoscale," *Circuits, Systems, and Signal Processing*, vol. 40, no. 11, pp. 5367-5380, 2021, doi: 10.1007/s00034-021-01719-4.

- [5] M. Noorallahzadeh and M. Mosleh, "Efficient designs of reversible shift register circuits with low quantum cost," *Journal of Circuits, Systems and Computers*, vol. 30, no. 12, p. 2150215, 2021, doi: 10.1142/S0218126621502157.

- [6] T. Liu *et al.*, "Efficient scheme for implementing a hybrid Toffoli gate with two NV ensembles simultaneously controlling a single superconducting qubit," *Applied Physics Letters*, vol. 123, no. 13, 2023, doi: 10.1063/5.0169902.

- [7] M. Noorallahzadeh and M. Mosleh, "Parity-preserving reversible flip-flops with low quantum cost in nanoscale," *The Journal of Supercomputing*, vol. 76, no. 3, pp. 2206-2238, 2020, doi: 10.1007/s11227-019-03074-3.

- [8] R. Landauer, "Irreversibility and heat generation in the computing process," *IBM journal of research and development*, vol. 5, no. 3, pp. 183-191, 1961, doi: 10.1147/rd.53.0183.

- [9] G. E. Moore, "Cramming more components onto integrated circuits," ed: McGraw-Hill New York, NY, USA:, 1965.

- [10] C. H. Bennett, "Logical reversibility of computation," *IBM journal of Research and Development*, vol. 17, no. 6, pp. 525-532, 1973, doi: 10.1147/rd.176.0525.

- [11] M. Noorallahzadeh and M. Mosleh, "Parity-preserving reversible flip-flops with low quantum cost in nanoscale," *The Journal of Supercomputing*, pp. 1-33, 2019, doi: 10.1007/s11227-019-03074-3.

- [12] S. Sayedsalehi, M. R. Azghadi, S. Angizi and K. Navi, "Restoring and non-restoring array divider designs in quantum-dot cellular automata," *Information sciences*, vol. 311, pp. 86-101, 2015, doi: 10.1016/j.ins.2015.03.030.

- [13] N. M. Nayeem, A. Hossain, M. Haque, L. Jamal and H. M. H. Babu, "Novel reversible division hardware," in 52nd IEEE International Midwest Symposium on Circuits and Systems, 2009, pp. 1134-1138, doi: 10.1109/MWSCAS.2009.5235968.

- [14] F. Dastan and M. Haghparast, "A novel nanometric fault tolerant reversible divider," *International Journal of Physical Sciences*, vol. 6, no. 24, pp. 5671-5681, 2011, doi: 10.5897/IJPS11.981.

- [15] H. M. H. Babu and M. S. Mia, "Design of a compact reversible fault tolerant division circuit," *Microelectronics Journal*, vol. 51, pp. 15-29, 2016, doi: 10.1016/j.mejo.2016.01.003.

- [16] M. Talebi, M. Mosleh, M. Haghparast and M. Chekin, "Effective scheme of parity-preserving-reversible floating-point divider," *The European Physical Journal Plus*, vol. 137, no. 9, pp. 1-13, 2022, doi: 10.1140/epjp/s13360-022-03212-6.

- [17] M. Valinataj, M. Mirshekar and H. Jazayeri, "Novel low-cost and fault-tolerant reversible logic adders," *Computers & Electrical Engineering*, vol. 53, pp. 56-72, 2016, doi: 10.1016/j.compeleceng.2016.06.008.

- [18] A. Sarker, H. M. Hasan Babu and S. M. M. Rashid, "Design of a DNA-based reversible arithmetic and logic unit," *IET nanobiotechnology*, vol. 9, no. 4, pp. 226-238, 2015, doi: 10.1049/iet-nbt.2014.0056.

- [19] B. Parhami, "Fault-tolerant reversible circuits," in 2006 fortieth asilomar conference on signals, systems and computers, 2006, pp. 1726-1729, doi: 10.1109/ACSSC.2006.355056.

- [20] E. PourAliAkbar, K. Navi, M. Haghparast and M. Reshadi, "Novel Optimum Parity-Preserving Reversible Multiplier Circuits," *Circuits, Systems, and Signal Processing,* vol. 39, no. 10, pp. 5148-5168, 2020, doi: 10.1007/s00034-020-01406-w

- [21] E. PourAliAkbar, K. Navi, M. Haghparast and M. Reshadi, "Novel Designs of Fast Parity-Preserving Reversible Vedic Multiplier," E. PourAliAkbar, K. Navi, M. Haghparast, and M. Reshadi, "Novel Designs of Fast Parity-Preserving Reversible Vedic Multiplier", *The CSI Journal on Computer Science and Engineering*, vol. 17, no. 1, 2019.

- [22] S. R. Arabani, M. R. Reshadinezhad and M. Haghparast, "Design of a parity preserving reversible full adder/subtractor circuit," *International Journal of Computational Intelligence Studies*, vol. 7, no. 1, pp. 19-32, 2018, doi: 10.1504/IJCISTUDIES.2018.090164.

- [23] N. K. Misra, B. Sen, S. Wairya and B. Bhoi, "Testable novel parity-preserving reversible gate and lowcost quantum decoder design in 1D molecular-QCA," *Journal of Circuits, Systems and Computers*, vol. 26, no. 09, p. 1750145, 2017, doi: 10.1142/S0218126617501456.

- [24] M. Haghparast and A. Bolhassani, "On design of parity preserving reversible adder circuits," *International Journal of Theoretical Physics*, vol. 55, no. 12, pp. 5118-5135, 2016, doi: 10.1007/s10773-016-3133-5.

- [25] R.-G. Zhou, Y.-C. Li and M.-Q. Zhang, "Novel designs for fault tolerant reversible binary coded decimal adders," *International Journal of Electronics*, vol. 101, no. 10, pp. 1336-1356, 2014, doi: 10.1080/00207217.2013.832388.

- [26] M. Islam and Z. Begum, "Reversible logic synthesis of fault tolerant carry skip BCD adder," *arXiv preprint arXiv:1008.3288*, 2010, doi: 10.48550/arXiv.1008.3288.

- [27] S. Hod, "Best approximation to a reversible process in black-hole physics and the area spectrum of spherical black holes," *Physical Review D*, vol. 59, no. 2, p. 024014, 1998, doi: 10.1103/PhysRevD.59.024014.

- [28] R. C. Merkle, "Two types of mechanical reversible logic," *Nanotechnology*, vol. 4, no. 2, p. 114, 1993, doi: 10.1088/0957-4484/4/2/007.

- [29] M. Noorallahzadeh, M. Mosleh and K. Datta, "A new design of parity-preserving reversible multipliers based on multiple-control toffoli synthesis targeting emerging quantum circuits," *Frontiers of Computer Science*, vol. 18, no. 6, p. 186908, 2024, doi: 10.1007/s11704-023-2492-3.

- [30] A. Bolhassani and M. Haghparast, "Optimised reversible divider circuit," *International Journal of Innovative Computing and Applications*, vol. 7, no. 1, pp. 13-33, 2016, doi: 10.1504/IJICA.2016.075465.

- [31] H. Thapliyal and N. Ranganathan, "Design of reversible sequential circuits optimizing quantum cost, delay, and garbage outputs," *ACM Journal on Emerging Technologies in Computing Systems (JETC)*, vol. 6, no. 4, pp. 1-31, 2010, doi: 10.1145/1877745.1877748.

- [32] M. Mohammadi and M. Eshghi, "On figures of merit in reversible and quantum logic designs," *Quantum Information Processing*, vol. 8, pp. 297-318, 2009, doi: 10.1007/s11128-009-0106-0.

- [33] A. Barenco *et al.*, "Elementary gates for quantum computation," *Physical review A*, vol. 52, no. 5, p. 3457, 1995, doi: 10.1103/PhysRevA.52.3457.

- [34] M. Morrison and N. Ranganathan, "Design of a reversible ALU based on novel programmable reversible logic gate structures," in *IEEE computer society annual symposium on VLSI*, 2011, pp. 126-131, doi: 10.1109/ISVLSI.2011.30.

- [35] M. Morrison and N. Ranganathan, "A novel optimization method for reversible logic circuit minimization," in *IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, 2013, pp. 182-187, doi: 10.1109/ISVLSI.2013.6654656.

- [36] D. M. Miller, M. Soeken and R. Drechsler, "Mapping NCV circuits to optimized Clifford+T circuits," in International Conference on Reversible Computation, 2014, pp. 163-175, doi: 10.1007/978-3-319-08494-7\_13.

- [37] M. Noorallahzadeh and M. Mosleh, "Efficient designs of reversible BCD to EX-3 Converter with low quantum cost in nanoscale," *International Journal of Quantum Information*, vol. 18, no. 05, p. 2050020, 2020, doi: 10.1142/S0219749920500203.

- [38] E. Fredkin and T. Toffoli, "Conservative logic," Int. J. of Theoretical Physics, vol. 21, pp. 219-253, 1982, doi: 10.1007/BF01857727.

- [39] M. Noorallahzadeh, M. Mosleh, S. S. Ahmadpour, J. Pal and B. Sen, "A new design of parity preserving reversible Vedic multiplier targeting emerging quantum circuits," *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, p. e3089, 2023, doi: 10.1002/jnm.3089.

- [40] B. K. Bhoi, N. K. Misra and M. Pradhan, "Synthesis and simulation study of non-restoring cell architecture layout in perpendicular nano-magnetic logic," *Journal of Computational Electronics*, vol. 19, no. 1, pp. 407-418, 2020, doi: 10.1007/s10825-019-01432-1.

- [41] M. Haghparast and K. Navi, "Novel reversible fault tolerant error coding and detection circuits," *International Journal of Quantum Information*, vol. 9, no. 02, pp. 723-738, 2011, doi: 10.1142/S0219749911007447.

- [42] A. Banerjee, "Reversible cryptographic hardware with optimized quantum cost and delay," in *Annual IEEE India Conference (INDICON)*, 2010, pp. 1-4, doi: 10.1109/INDCON.2010.5712605.

#### COPYRIGHTS

©2025 by the authors. Published by the Islamic Azad University Bushehr Branch. This article is an openaccess article distributed under the terms and conditions of the Creative Commons Attribution 4.0 International (CC BY 4.0) <u>https://creativecommons.org/licenses/by/4.0</u>