Journal of Optoelectronical Nanostructures

Summer 2022 / Vol. 7, No. 3

# **Research Paper**

# A Robust Single Layer QCA Decoder Using a Novel Fault Tolerant Three Input Majority Gate

## Samira Riki<sup>1</sup>, Fatemeh Serajeh Hassani<sup>2</sup>

<sup>1</sup>Department of Computer Engineering, Higher Education Complex of Saravan, Saravan, Iran

<sup>2</sup>Department of Computer Engineering, Sharif University of Technology, Tehran, Iran

Received: 4 Jun 2022 Revised: 1 Jul. 2022 Accepted: 5 Jul. 2022 Published: 15 Sep 2022

Use your device to scan and read the article online

Keywords: Majority Gate, Decoder, Reliability, Fault Tolerant, Quantum-dot Cellular Automata.

Coplanar

Abstract Quantum-dot Cellular Automata (QCA) is an emerging technology and one of the suitable alternatives to conventional CMOS technology. Designing efficient basic logic circuits like decoders is an open research topic in this emerging technology. As reliability is also the most important issue in QCA technology circuit design due to its susceptibility to faults occurring during chemical fabrication, we design an efficient coplanar robust 2-to-4 decoder, employing a novel fault-tolerant three-input majority gate. Our proposed majority gate is designed with 11 simple QCA cells. The area and energy consumptions of the proposed majority gate is 0.01  $\mu$ m<sup>2</sup> and  $1.49 \times 2^{-2}$  MeV, respectively. The presented majority gate has also 71% and 100% tolerance against single-cell omission and extra-cell deposition defects, respectively, and it has a proper tolerance against cell displacement and misalignment defects. The novel robust 2-to-4 decoder is also designed using the proposed majority gate. The simulation results show that the presented decoder is more efficient in comparison to previous designs.

Citation: Samira Riki, Fatemeh Serajeh Hassani. A Robust Single Layer QCA Decoder Using A Novel Fault Tolerant Three Input Majority Gate .

- Journal of Optoelectronical Nanostructures. 2022; 7 (3): 23-45

- DOI: 10.30495/JOPN.2022.29904.1258 \*Corresponding author: Samira Riki

Address: Department of Computer Engineering, Higher Education Complex of Saravan, Saravan, Iran. Tell: 05437631017 Email: s.riki@saravan.ac.ir

## **1. INTRODUCTION**

24

CMOS is one of the most popular technologies for designing integrated circuits. The number of transistors in a dense integrated circuit doubles every 18 months due to the Moore's law [1]. As a result, the transistor dimensions become halved. On the other hand, as the transistor shrinks, it reaches the physical limitation. This issue causes some serious disturbances in digital circuit operations. Researchers have been trying a lot to find a suitable alternative to CMOS. Spintronics [2] and quantum-dot cellular automata (QCA) [3-6] are the technologies that have been introduced as two appropriate replacements for CMOS. Considering the area, latency, and power consumption parameters of QCA technology, it can be the best alternative to CMOS [7-11, 45, 47].

QCA technology was introduced by Lent et al. in 1993 [12]. There is no electrical current in this technology and information is transformed through the Coulomb interactions of electrons in quantum cells. One of the challenges in designing QCA circuits is the defects that may occur during the chemical synthesis and deposition phases [14].

The most important possible defects that reduce the efficiency of the QCA circuits are cell omission, cellular displacement, cell misalignment, and extra cells deposition [13-16]. Therefore, QCA researchers have been looking for different ways of designing fault-tolerant circuits.

Decoders are known computational circuits which are widely used in different digital circuit designs. We propose a fault-tolerant majority gate in order to design a robust decoder circuit based on it. The majority gate is the most important basic gate in QCA technology and all QCA circuits can be designed and implemented using the majority gates and inverters.

In this study, we first propose a fault-tolerant three-input majority gate with 11 simple QCA cells. Then the functionality of the introduced majority gate is verified via physical proof. The proposed majority gate is then investigated against cell omission, extra cell deposition, and cell displacement defects. Then the energy consumption of the proposed majority gate is calculated and compared with the similar types of majority gates. Afterward, a fault-tolerant 2-to-4 decoder is introduced using the proposed majority gate and finally, we conclude the study.

The remainder of the paper is structured as follows. We review the basic concepts in QCA technology in Section 2. The proposed fault-tolerant three-input majority gate, its functionality verification, and reliability analysis are studied in Section 3. Section 4 introduces a robust 2-to-4 decoder based on the proposed majority gate. Finally, we conclude in Section 5.

#### Samira Riki et al

25

## 2. BASIC CONCEPTS IN QCA TECHNOLOGY

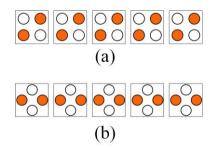

A QCA cell has a square shape that contains four quantum dots located in its vertices. A pair of electrons move freely between the quantum dots inside the cell. Generally, there are six possible states to place an electron pair in four holes, but not all of them are stable. In fact, due to the Coulumbic repulsion between the electrons, they are always placed in two square diameters of a QCA cell which are illustrated in Figure 1. These two configurations are the -1 and +1 polarizations which are defined as the binary values of 0 and 1, respectively [17, 40].

Fig. 1. The two stable states of quantum cells.

QCA cells can be placed next to each other to form different circuits. A QCA wire is created by putting the cells in a linear array form. Figure 2 shows two different types of QCA wires. As they are shown the direct and rotated QCA wires consist of simple and rotated cells, respectively [41].

Fig. 2. QCA wires. a) direct mode, b) rotated mode.

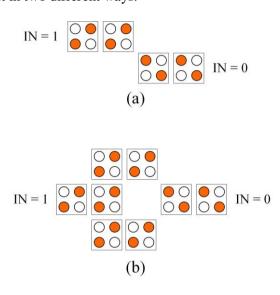

In QCA technology, the majority gates and inverters are the two main logic gates which are widely employed to implement almost all types of logic circuits. Generally, there are two different designs for inverter which are used in QCA

circuits (Figure 3). Figure 3.b illustrates a reliable inverter that transmits the input to the output in two different ways.

Fig. 3. The QCA inverter designs: a) the simple structure, b) the robust structure.

Figure 4 shows two different designs for a three-input majority gate. The output of this gate is calculated based on Eq.1. This gate consists of five QCA cells including three input cells, one output cell, and a decision-maker which is located in the middle of the gate. If at least two inputs out of all the three inputs become one, the output would be one; otherwise, the output would be zero [39].

$$MV3(X, Y, Z) = (X \land Y) \lor (X \land Z) \lor (Y \land Z)$$

(1)

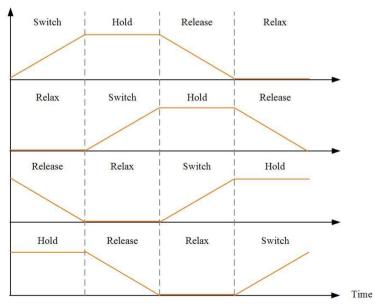

The QCA circuits need a clocking system to work properly. The clocking system is responsible to supply the main circuit power and controlling the data propagation in quantum cells. The clocking system also facilitates electrons movement in the cell and does not let them tunnel between the quantum dots. Each QCA cell may have one of these following four clock phases: switch, hold, release or relax. A cell in the switch phase starts its calculations. In the hold phase, electrons are stored and positioned within a quantum dot based on the polarity of adjacent cells. In the release phase, the electrons begin to leave their place of residence, and in the relax phase, they completely leave the place of residence and can easily circulate inside the cell. QCA designs have four clock

Inter-dot Barrier

27

signals, each of which is 90 degrees different from the phase of the next and previous clocks. For example, when clock 1 is in the switch phase, clock 2 is in the relax phase, clock 3 is in the release phase, and finally, clock 4 is in the hold phase. Figure 5 shows these four clock signals.

Fig. 4. Three input majority gate designs: a) the original majority gate, b) the rotated majority gate.

Fig. 5. Four states of clocks in QCA.

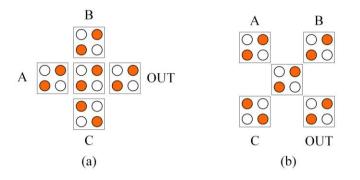

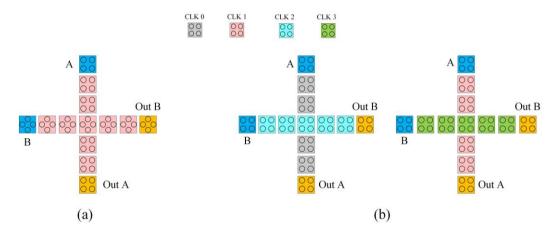

There are three types of wire crossing in QCA designs: multilayer, coplanar, and clock-based coplanar. The QCA wires in multilayer wire crossing are in different layers. Since the implementation of this type of wire crossing is practically impossible, coplanar and clock-based coplanar wire crossing structures have been proposed. Figure 6.a illustrates the coplanar wire crossing. As it is shown one of the two crossing wires is based on simple QCA cells and the other is based on rotated QCA cells. On the other hand, both crossing wires in clock-based coplanar wire crossing are based on simple QCA cells but with different clock phases (Figure 6.b). In this type of wire crossing, one of the wires must be designed in switch or release clock phases and the other must be in the hold or relax clock phases [42].

Fig. 6. Wire crossing in QCA: a) coplanar, b) coplanar clocking based

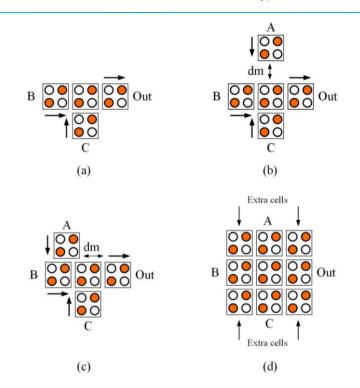

One of the most important issues in QCA technology is designing robust circuits against faults that may occur during the synthesis and chemical deposition steps. Common defects in QCA technology are divided into four categories: cell omission, cell displacement, cell misalignment, and extra cell deposition [18-20]. Cell omission defect occurs when a cell is missing compared to fault-free design (Figure 7.a). Cell displacement defect occurs when a cell is displaced from its original location (Figure 7.b). Cell misalignment defect occurs when the balance of the cells is disturbed (Figure 7.c). Finally, an extra cell deposition defect occurs when an additional cell is placed in the main structure (Figure 7.d).

29

Fig. 7. Different kinds of defects: a) cell omission, b) cell displacement, c) cell misalignment, d) extra cell deposition.

#### **3.** THE PROPOSED THREE INPUT MAJORITY GATE

The three-input majority gate is one of the most important and basic gates in QCA technology since all types of digital circuits can be implemented using a combination of the majority and inverter gates. The area and energy-efficient robust circuits can be designed using fault-tolerant three-input majority gates with optimal area and energy consumptions. In this section, we first propose a fault-tolerant three-input majority gate and verify its functionality using QCA Designer 2.0.3 [21] simulator and physical proof (Kink energy). The proposed gate is then examined in terms of tolerance against cell omission, extra cell deposition, and cell displacement. After that, we compare our proposed gate with the previous majority gates.

The proposed three-input majority gate has 11 simple QCA cells and its area is 0.01  $\mu$ m<sup>2</sup>. The energy consumption of the proposed gate is also 1.49×e-002 MeV which is calculated by the QCA Designer-E simulator [30].

Fig. 8. a) The proposed fault tolerant three input majority gate, b) the proposed AND gate, c) the proposed OR gate.

Fig. 9. The simulation results of the proposed majority gate.

31

Figure 8.a illustrates the proposed majority gate. As it can be seen, the output is generated during one clock phase. The simulation results of our proposed majority gate that is obtained from QCA Designer 2.0.3 are also shown in Figure 9. Two-input AND logic gates and OR logic gates can also be produced based on the proposed majority gate (Figure 8.b,c).

## A. Performance evaluation using Kink energy

In this subsection we want to evaluate the proposed three-input majority gate using Kink energy. Since the majority gate has three inputs so it would have eight different modes which results in large number of calculations. In the following, we only consider the gate accuracy for the input mode (A, B, C) = (1, 0, 1). It is assumed that the quantum cells dimensions are 18 nm \* 18 nm and the distance between two adjacent cells is 2 nm. The following formula is the one that calculate the energy between the electrons (Kink energy) [22, 23]:

$$\mathbf{U} = \frac{\mathbf{k}\mathbf{q}_1\mathbf{q}_2}{\mathbf{r}}(\mathbf{J}) \tag{2}$$

In the mentioned formula, U represents the Kink energy, k is the Coulomb constant, q1 and q2 are the energy of the electrons, and r is the distance between the two electrons. By placing k and q, the resulting Kink energy is measured using the following formula:

$$\mathbf{U} = \frac{9 \times 10^9 \times 1.6 \times 10^{-38}}{r} = \frac{23.04 \times 10^{-29}}{r}$$

(3)

**Table 1**: The Kink energy between electrons  $e_1$  to  $e_4$  with electrons  $e_x$  and  $e_y$  in fig. 10.aand fig. 10.b

| Figur                         | e 10.a                        | Figur                          | e 10.b                         |

|-------------------------------|-------------------------------|--------------------------------|--------------------------------|

| Electron x                    | Electron y                    | Electron x                     | Electron y                     |

| $Ue_1 = 1.15 \times 10^{-20}$ | $Ue_1 = 1.27 \times 10^{-20}$ | $Ue_1 = 11.52 \times 10^{-20}$ | $Ue_1 = 0.86 \times 10^{-20}$  |

| $Ue_2 = 0.55 \times 10^{-20}$ | $Ue_2 = 1.15 \times 10^{-20}$ | $Ue_2 = 0.86 \times 10^{-20}$  | $Ue_2 = 0.61 \times 10^{-20}$  |

| $Ue_3 = 1.15 \times 10^{-20}$ | $Ue_3 = 0.55 \times 10^{-20}$ | $Ue_3 = 0.61 \times 10^{-20}$  | $Ue_3 = 0.86 \times 10^{-20}$  |

| $Ue_4 = 1.27 \times 10^{-20}$ | $Ue_4 = 1.15 \times 10^{-20}$ | $Ue_4 = 0.86 \times 10^{-20}$  | $Ue_4 = 11.52 \times 10^{-20}$ |

| $U_T = 8.24 \times 10^{-20}$  |                               | $U_T = 27.7 \times 10^{-20}$   |                                |

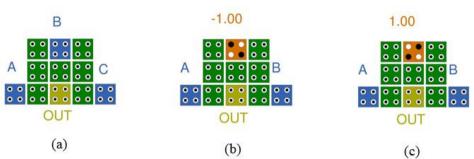

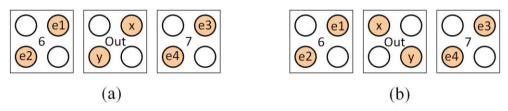

There are two possible arrangements of electrons by applying the input vector (A, B, C) = (1, 0, 1) to the proposed gate at a radius of less than 20 nm which are shown in Figure 10. We want to find the state in which the electrons are

more stable. First, the Kink energy of the electrons  $e_1$  to  $e_4$  by the electrons  $e_x$  and  $e_y$  are calculated using the Eq3 for the two states a and b in Figure 10. Table 1 shows the calculation results. As it is shown as the total Kink energy related to Figure 10.a is less than Figure 10.b, the output cell in Figure 10.a is more stable than Figure 10.b which confirms the correct direction of the output cell.

Fig. 10. a) Binary '1' output and b) binary '0' output.

## **B.** Fault tolerance analysis through simulation

In this subsection, the circuit tolerance against possible defects such as singlecell omission, double cell omission, cell misalignment, and extra cell deposition is examined using QCA Designer 2.0.3 simulator.

One of the most likely defects in QCA technology is cell omission. Cell omission defect happens when one cell or more are missing compared to the fault-free design. Table 2 And Table 3 show the circuit output in all possible cases of single-cell and double-cell omission defects. According to these tables, if a single cell is deleted the output would be correct in five cases out of all possible seven cases and if two cells are removed, the output of six cases out of all 21 possible cases would be correct. So, if a single cell or two cells are omitted from the proposed majority gate the output would be 71% (= 5/7) and 29% (= 6/21) correct, respectively.

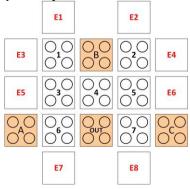

Fig. 11. Extra cells around the proposed majority gate.

Journal of Optoelectronical Nanostructures. 2022; 7 (3): 23-45

#### Samira Riki et al

33

In order to check the extra cell deposition defect, we place simple QCA cells all around the proposed majority gate as it is shown in Figure 11. The proposed gate output results after placing extra cells are in Table 4. According to this table, the output of the proposed gate is correct in all cases. Therefore, the tolerance of the proposed gate against additional cell deposition defects is 100%. In the following, an attempt has been made to investigate the effect of misalignment and displacement defects on the proposed gate. Table 5 shows the permitted displacement of all cells. As the results are shown, the proposed gate has a high tolerance against these defects.

| Omitted cell | Output  | Omitted cell       | Output    |

|--------------|---------|--------------------|-----------|

| 1            | Correct | 5                  | Correct   |

| 2            | Correct | 6                  | Incorrect |

| 3            | Correct | 7                  | Incorrect |

| 4            | Correct | Correct rate = 71% |           |

Table 2 : The output of the proposed gate when single cell omission ocurred

Table 3: The output of the proposed gate when double cell omission ocurred

| Omitted cells | Output    | Omitted cells      | Output    |

|---------------|-----------|--------------------|-----------|

| 1,2           | Correct   | 3,4                | Incorrect |

| 1,3           | Correct   | 3,5                | Correct   |

| 1,4           | Incorrect | 3,6                | Incorrect |

| 1,5           | Correct   | 3,7                | Incorrect |

| 1,6           | Incorrect | 4,5                | Incorrect |

| 1,7           | Incorrect | 4,6                | Incorrect |

| 2,3           | Correct   | 4,7                | Incorrect |

| 2,4           | Incorrect | 5,6                | Incorrect |

| 2,5           | Correct   | 5,7                | Incorrect |

| 2,6           | Incorrect | 6,7                | Incorrect |

| 2,7           | Incorrect | Correct rate = 29% |           |

C. The proposed majority gate comparing to previous works

There are a large number of fault-tolerant three-input majority gates which have already been proposed. In this subsection, we compare our proposed majority gate with a group of best introduced majority gates. Table 6 summarizes the key characteristics of our proposed gate in comparison to the best related works.

| Position   | Output     |

|------------|------------|

| E1         | Correct    |

| E2         | Correct    |

| E3         | Correct    |

| E4         | Correct    |

| E5         | Correct    |

| E6         | Correct    |

| E7         | Correct    |

| E8         | Correct    |

| Correct ra | ite = 100% |

**Table 4:** The proposed gate output when extra cell deposition defect occurred

Table 5: The permissible range of cells displacement in the proposed majority gate

| Cell | North         | South            | West          | East          |

|------|---------------|------------------|---------------|---------------|

|      | ( <b>nm</b> ) | ( <b>nm</b> )    | ( <b>nm</b> ) | ( <b>nm</b> ) |

| Α    | $\leq 3$      | $\leq 3$         | $\leq 1$      | -             |

| В    | $\leq 9$      | -                | -             | -             |

| С    | ≤3            | <u>≤</u> 3<br>≤6 | -             | ≤1            |

| OUT  | -             | ≤6               | -             | -             |

| 1    | 8             | -                | 8             | -             |

| 2    | 8             | -                | -             | 8             |

| 3    | -             | -                | 8             | -             |

| 5    | -             | -                | -             | 8             |

| 6    | -             | ≤4               | -             | -             |

| 7    | -             | <u>≤</u> 4<br>≤4 | -             | -             |

| ~                                       |

|-----------------------------------------|

| gates                                   |

| majority                                |

| QCA                                     |

| t robust                                |

| of best                                 |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

| Key characteristic                      |

| : Key                                   |

| Ö                                       |

| Table                                   |

Samira Riki et al

|                          |              |                |                            |                              |                           |                                                                                     |                         | Tolerance Against Faults (%)                 | ainst Faults | (%)                                     |

|--------------------------|--------------|----------------|----------------------------|------------------------------|---------------------------|-------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|--------------|-----------------------------------------|

| Majority<br>Gate         | Cell<br>Type | #Cell<br>Count | Area<br>(um <sup>2</sup> ) | Latency<br>(clock<br>cycles) | 1 otal<br>Energy<br>(meV) | Average<br>Energy<br>(meV)                                                          | Single Cell<br>Omission | Single Cell Double Cell<br>Omission Omission |              | Extra Cell Cell Deposition Displacement |

| [24]                     | rotated      | 13             | 0.01                       | 0.25                         | 4.87×<br>e-003            | $\begin{array}{c} 4.43 \times e-\\ 004 \end{array}$                                 | 88                      | 39.5                                         | 100          | $0.1$ - $\infty$                        |

| [25]                     | rotated      | 10             | 0.01                       | 0.25                         | 6.83 ×<br>e-004           | $\begin{array}{c} \textbf{6.21}\times\textbf{e}\text{-}\\ \textbf{005} \end{array}$ | 100                     | 80                                           | 06           | 5 - ∞                                   |

| [26]                     | simple       | 25             | 0.02                       | 0.25                         | 1.57×<br>e-002            | $1.42 \times e$ - $003$                                                             | 80                      | 36                                           | undefined    | undefined                               |

| [27]                     | simple       | 37             | 0.05                       | 0.25                         | 9.32×<br>e-003            | $\begin{array}{c} 8.48\times e-\\ 004 \end{array}$                                  | 82                      | 66                                           | 50           | 3 - 14                                  |

| [28]                     | simple       | 36             | 0.05                       | 0.25                         | 2.31×<br>e-002            | 2.1 	imes e- $003$                                                                  | 93.8                    | 66                                           | undefined    | undefined                               |

| [29]                     | simple       | 20             | 0.03                       | 0.5                          | 1.96×<br>e-002            | $\begin{array}{c} 1.78 \times e-\\ 003 \end{array}$                                 | 87                      | 60                                           | 100          | 5.2 - 500                               |

| [43]                     | simple       | 27             | 0.02                       | 0.25                         | $1.8 \times e$ - $002$    | $\begin{array}{c} 1.64 \times \mathrm{e}\text{-}\\ 003 \end{array}$                 | 100                     | 85                                           | 100          | 4 - ∞                                   |

| [44]-first<br>structure  | simple       | 13             | 0.01                       | 0.25                         | 1.76×<br>e-002            | $\begin{array}{c} 1.6 \times \mathrm{e}\text{-}\\ 003 \end{array}$                  | 88                      | 41                                           | 100          | 1.5 - $\infty$                          |

| [44]-second<br>structure | simple       | 18             | 0.02                       | 0.25                         | 1.52×<br>e-002            | $\begin{array}{c} 1.38 \times \mathrm{e}\text{-}\\ 003 \end{array}$                 | 91                      | 62                                           | 100          | 3 - ∞                                   |

| proposed                 | Simple       | 11             | 0.01                       | 0.25                         | 1.49×<br>e-002            | $\begin{array}{c} 1.35 \times \mathrm{e}\text{-}\\ 003 \end{array}$                 | 71                      | 29                                           | 100          | 3 - ∞                                   |

As it is shown in Table 6 the majority gates proposed in [26-29, 43, 44] were designed using only simple QCA cells but [24, 25] have presented some other majority gates which are based on both simple and rotated QCA cells. As mentioned before, the rotated QCA cells decrease the robustness of QCA designs since they are more susceptible to faults during the fabrication process. Therefore, our proposed gate is more reliable than [24, 25] works.

Comparing our proposed majority gate to those previous works which only employed simple OCA cells, it has lower cell count, area, and energy consumptions and in most cases with an average better tolerance against common OCA faults.

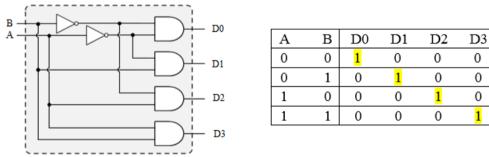

#### 4. THE PROPOSED DECODER

A decoder is a combinational logic circuit that converts n coded inputs to 2n unique outputs. Decoders are widely employed in many applications and play an important role in many electronic circuit designs including lookup tables and random-access memories [31-33]. Optical decoders are also employed widely in optical logic circuits [45, 48]. Therefore, it is very important to design and implement a fault-tolerant decoder that is optimal in terms of energy consumption and area. Figure 12 shows the truth table and digital circuit design of a 2-to-4 decoder.

Fig. 12. Digital circuit design and truth table of a 2-to-4 decoder

In the proposed decoder, four majority gates are used as Eq.4 order to make the outputs:

D0 = MV(0, A', B')D1 = MV(0, A', B)D2 = MV(0, A, B')D3 = MV(0, A, B)

(4)

0

0

0

#### Samira Riki et al

37

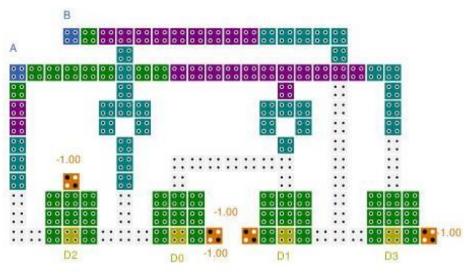

Figure 13 illustrates a 2-to-4 decoder circuit design based on the proposed majority gate. As it is shown the relevant circuit has two inputs named A and B and produces four outputs which are D0, D1, D2, and D3. The proposed decoder is simulated and verified with QCA Designer 2.0.3 simulator. The layout and simulation results of the proposed decoder are shown in Figure 13 and Figure 14, respectively.

Each majority gate of the proposed circuit needs a clock phase to operate properly and the decoder output is ready after five clocks. The introduced single-layer decoder circuit has 137 cells which is more area efficient in comparison to the other proposed coplanar decoders. The simulation results show that only one of the decoder outputs has a value of one in each clock and the rest of the outputs are zero which is proof of the functional correctness of the proposed decoder.

| Decoder<br>circuits | Crossover<br>type | Number of<br>majority<br>gates | Cell count | Area (um <sup>2</sup> ) | Fault<br>tolerant |

|---------------------|-------------------|--------------------------------|------------|-------------------------|-------------------|

| [34]                | coplanar          | 8                              | 270        | 0.38                    | -                 |

| [35]                | coplanar          | 8                              | 296        | 0.43                    | -                 |

| [36]                | coplanar          | 6                              | 212        | 0.25                    | -                 |

| [37]                | coplanar          | 4                              | 193        | 0.22                    | -                 |

| First design        | coplanar          | 4                              | 110        | 0.13                    | -                 |

| [38]                |                   |                                |            |                         |                   |

| Second              | coplanar          | 4                              | 159        | 0.18                    | -                 |

| design [38]         |                   |                                |            |                         |                   |

| [31]                | multilayer        | 4                              | 100        | 0.09                    | -                 |

| First design        | coplanar          | 6                              | 56         | 0.05                    | -                 |

| [46]                |                   |                                |            |                         |                   |

| Second              | Multilayer        | 6                              | 62         | 0.05                    | -                 |

| design [46]         |                   |                                |            |                         |                   |

| Proposed            | coplanar          | 4                              | 137        | 0.15                    | $\square$         |

Table 7. Characteristics analysis of the 2 to 4 decoders

Table 7 compares the presented decoder to already introduced decoders. This comparison is performed in terms of crossover type, the number of majority gates, the number of cells, occupied area, and fault tolerance. As it is shown, works that are introduced in [34-37] consume more cell count and area in comparison to our proposed decoder.

Fig. 13. The QCA layout of the proposed 2-to-4 decoder

Fig. 14. The simulation results of the proposed 2-to-4 decoder

There are two different designs that were proposed in each [38] and [46] work. While the second design of [38] consumes more area, the first design of [38] and both designs of [46] are area efficient comparing to our work. But none of the first and second designs in [38] and [46] are fault-tolerant. The presented decoders in [31] and the second design in [46] are multilayer designs which increase the fabrication overheads. In fact, our proposed decoder is the only fault-tolerant coplanar design which is area efficient in comparison to most of the previous works.

## **5. CONCLUSION**

One of the most important and suitable alternatives to CMOS is the QCA technology due to its high density, low power, and high-speed characteristics. Fault tolerant circuit design is the most important issue in QCA technology. In this paper, we have proposed a coplanar robust 2-to-4 decoder based on a novel fault-tolerant three-input majority gate using the QCA technology. The proposed majority gate has 71% and 100% tolerance against single-cell omission and extra-cell deposition defects, respectively with a suitable tolerance against cell displacement and misalignment defects. We have finally designed a coplanar area and energy-efficient robust 2-to-4 decoder using the presented majority gate.

## **CONFLICT OF INTEREST**

39

The authors state that publication of this manuscript does not involve any conflicts of interest.

REFERENCES

- [1] Mack, C. A. Fifty years of Moore's law. IEEE Transactions on semiconductor manufacturing, 24(2) (2011) 202-207. Available:http://www.intel .in/conte nt/www/in/en/silic on-innov ation s/moore s-law-techn ology .html. Accessed 20 Feb 2020

- [2] Zhang H et al .Spintronic processing unit within voltage-gated spin hall effect MRAMs. IEEETrans Nanotechnol 18 (2019) 473–483. Available:<u>https://ieeexplore.ieee.org/document/8706951</u>

- [3] Babaie S, Sadoghifar A, Bahar. AN Design of an efficient multilayer arithmetic logic unit in quantum-dot cellular automata (QCA). IEEE Trans Circuits Syst II Express Briefs 66(6) (2018) 963–967. Available:<u>https://ieeexplore.ieee.org/document/8480639</u>

- [4] Seyedi S, Ghanbari A, Navimipour NJ, New design of a 4-bit ripple carry adder on a nanoscale quantum-dot cellular automata. Mosc Univ Phys Bull 74(5) (2019) 494–501. Available:

https://link.springer.com/article/10.3103/S0027134919050126

[5] Seyedi S, Darbandi M, Navimipour NJ, Designing an efficient fault tolerance D-latch based on quantum-dot cellular automata nanotechnology. Optik 185 (2019) 827–837. Available:

https://doi.org/10.1016/j.ijleo.2019.03.029

[6] Fam SR, Navimipour NJ .Design of a loop-based random access memory based on the nanoscale quantum dot cellular automata. Photon Netw Commun 37(1) (2019) 120–130. Available:

https://link.springer.com/article/10.1007/s11107-018-0801-9

[7] Rigi, R., Navi, K., & Sharifi, H. Research Paper PhC-based Majority Gate using a nonlinear directional coupler. Journal of Optoelectronical Nanostructures, 6(4) (2021) 21-32.

Available:<u>http://jopn.marvdasht.iau.ir/article\_5039\_9a59d5bab7d8d307cf735</u> <u>e5de0becca1.pdf</u>

[8] Seyedi S, Navimipour NJ .An optimized three-level design of decoder based on nanoscale quantum-dot cellular automata. Int J Theor Phys 57(7) (2018) 2022–2033. Availabl:

https://link.springer.com/article/10.1007/s10773-018-3728-0

Journal of Optoelectronical Nanostructures. 2022; 7 (3): 23-45

[9] Seyedi S, Navimipour NJ. Design and evaluation of a new structure for faulttolerance fulladder based on quantum-dot cellular automata. Nano Commun Netw 16 (2018) 1–9. Available:

https://doi.org/10.1016/j.nancom.2018.02.002

[10] Gadim MR, Navimipour NJ. A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst Technol 24 (2018) 1–11. Available:

https://link.springer.com/article/10.1007/s00542-017-3502-x

[11] Safoev, N., & Jeon, J. C. A novel controllable inverter and adder/subtractor in quantum-dot cellular automata using cell interaction based XOR gate. Microelectronic Engineering, 222 (2020) 111197. Available:

https://doi.org/10.1016/j.mee.2019.111197

[12] Lent CS et al. Quantum cellular automata. Nanotechnology 4(1) (1993) 49. Available:

https://link.springer.com/chapter/10.1007/978-1-4615-0437-5\_10

[13] Tahoori MB et al. Defects and faults in quantum cellular automata at nano scale. In: 22<sup>nd</sup> IEEE VLSI Test Symposium. Proceedings. IEEE (2004). Available:

https://ieeexplore.ieee.org/document/1299255/

- [14] Ahmadpour S-S, Mosleh M, Heikalabad SR. An efficient fault-tolerant arithmetic logic unit using a novel fault-tolerant 5-input majority gate in quantum-dot cellular automata. Comput Electr Eng 82 (2020) 106548. Available: <u>https://doi.org/10.1016/j.compeleceng.2020.106548</u>

- [15] Momenzadeh M et al. Quantum cellular automata: new defects and faults for new devices. In: 18th International Parallel and Distributed Processing Symposium, 2004. Proceedings. IEEE10. Available:

https://ieeexplore.ieee.org/document/1303234

- [16] Seyedi S, Navimipour NJ. An optimized design of full adder based on nanoscale quantum-dot cellular automata. Opt Int J Light Electron Opt 158 (2017) 243–256. Available: <u>https://doi.org/10.1016/j.ijleo.2017.12.062</u>

- [17] Lent CS, Tougaw PD. A device architecture for computing with quantum dots. Proc IEEE 85(4) (1997) 541–557. Available:

https://ieeexplore.ieee.org/document/573740

[18] Ahmadpour SS, Mosleh M, Rasouli Heikalabad S. Robust QCA full-adders using an efficient fault-tolerant five-input majority gate. Int J Circuit Theory Appl 47 (2019) 1037–1056. Available:

https://onlinelibrary.wiley.com/doi/abs/10.1002/cta.2634

- [19] Hosseinzadeh H, Heikalabad SR. A novel fault tolerant majority gate in quantum-dot cellular automata to create a revolution in design of fault tolerant nanostructures, with physical verification. Microelectron Eng 192 (2018) 52–60. Available: <u>https://doi.org/10.1016/j.mee.2018.01.019</u>

- [20] Huang J, Momenzadeh M, Lombardi F. On the tolerance to manufacturing defects in molecular QCA tiles for processing-by-wire. J Electron Test 23(2) (2007) 163–174. Available:

https://link.springer.com/article/10.1007/s10836-006-0548-6

- [21] Walus K et al. QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1) (2004) 26–31. Available: <u>https://ieeexplore.ieee.org/document/1278264</u>

- [22] Ahmadpour S-S, Mosleh M, Heikalabad SR. A revolution in nanostructure designs by proposing a novel QCA full-adder based on optimized 3-input XOR. Physica B 550 (2018) 383–392. Available:

https://doi.org/10.1016/j.physb.2018.09.029

[23] Ahmadpour SS, Mosleh M. A novel ultra-dense and low-power structure for fault-tolerant three-input majority gate in QCA technology. Concurr Comput Pract Exp 32(5) (2019) e5548. Available:

https://onlinelibrary.wiley.com/doi/abs/10.1002/cpe.5548

[24] Moghimizadeh, T. and Mosleh, M. A novel design of fault-tolerant RAM cell in quantum-dot cellular automata with physical verification. The Journal of Supercomputing, 75(9) (2019) pp.5688-5716. Available:

https://link.springer.com/article/10.1007/s11227-019-02812-x

[25] Ahmadpour, S.S., Mosleh, M. and Rasouli Heikalabad, S. The design and implementation of a robust single-layer QCA ALU using a novel fault-tolerant three-input majority gate. Journal of Supercomputing, 76(12) (2020). Available:

42

https://link.springer.com/article/10.1007/s11227-020-03249-3

Journal of Optoelectronical Nanostructures. 2022; 7 (3): 23-45

[26] Sun, M., Lv, H., Zhang, Y. and Xie, G. The fundamental primitives with fault-tolerance in quantum-dot cellular automata. Journal of Electronic Testing, 34(2) (2018) pp.109-122. Available:

https://link.springer.com/article/10.1007/s10836-018-5723-z

- [27] Foroutan, S.A.H., Sabbaghi-Nadooshan, R., Mohammadi, M. and Tavakoli, M.B. Investigating multiple defects on a new fault-tolerant three-input QCA majority gate. The Journal of Supercomputing, (2021) 1-21. Available: <u>https://link.springer.com/article/10.1007/s11227-020-03567-6</u>

- [28] Wang, X., Xie, G., Deng, F., Quan, Y. and Lü, H. Design and comparison of new fault-tolerant majority gate based on quantum-dot cellular automata. Journal of Semiconductors, 39(8) (2018) p.085001. Available:

https://iopscience.iop.org/article/10.1088/1674-4926/39/8/085001

[29] Kumar, D. and Mitra, D. Design of a practical fault-tolerant adder in QCA. Microelectronics Journal, 53 (2016) 90-104. Available:

https://doi.org/10.1016/j.mejo.2016.04.004

[30] Torres, F.S., Wille, R., Niemann, P. and Drechsler, R. An energy-aware model for the logic synthesis of quantum-dot cellular automata. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 37(12) (2018) 3031-3041. Available:

https://ieeexplore.ieee.org/abstract/document/8246526

[31] Pourtajabadi, R., & Nayeri, M. A novel design of a multi-layer 2: 4 decoder using quantum-dot cellular automata. Journal of Optoelectronical Nanostructures, 4(1) (2019) 39-50. Available:

http://jopn.marvdasht.iau.ir/article\_3384.html

- [32] H. Balijepalli, and M. Niamat. Design of a nanoscale quantum-dot cellular automata configurable logic block for FPGAs. Circuits and Systems (MWSCAS), 2012 IEEE 55th International Midwest Symposium on. IEEE, (2012) 622-625. Available: <u>https://ieeexplore.ieee.org/document/6292097/</u>

- [33] P. P. Chougule, B. Sen, and T. D. Dongale. Realization of processing Inmemory computing architecture using quantum dot cellular automata. Microprocessors and Microsystems, 52, (Jul. 2017) 49-58. Available:

https://doi.org/10.1016/j.micpro.2017.04.022

- [34] Kianpour, M., & Sabbaghi-Nadooshan, R. A conventional design and simulation for CLB implementation of an FPGA quantum-dot cellular automata. Microprocessors and Microsystems, 38(8) (2014) 1046-1062. Available:https://doi.org/10.1016/j.micpro.2014.08.001

- [35] Sabbaghi-Nadooshan, R. A novel quantum-dot cellular automata CLB of FPGA. Journal of Computational Electronics, 13(3) (2014) 709-725. Available: <u>https://link.springer.com/article/10.1007/s10825-014-0590-z</u>

- [36] Kumar, M., & Sasamal, T. N. An Optimal design of 2-to-4 Decoder circuit in coplanar Quantum-dot cellular automata. Energy Procedia, 117 (2017) 450-457. Available:<u>https://doi.org/10.1016/j.egypro.2017.05.170</u>

- [37] Sherizadeh, R., & Navimipour, N. J. Designing a 2-to-4 decoder on nanoscale based on quantum-dot cellular automata for energy dissipation improving. Optik, 158 (2018) 477-489. Available:

https://doi.org/10.1016/j.ijleo.2017.12.055

[38] K. Makanda, and J. C. Jeon. Combinational Circuit Design Based on Quantum-Dot Cellular Automata. International Journal of Control and Automation 7(6). (Jun. 2014). 369-378.

Available: http://article.nadiapub.com/IJCA/vol7\_no6/34.pdf

[39] Majeed, A. H., Zainal, M. S. B., Alkaldy, E., & Nor, D. M. Full adder circuit design with novel lower complexity XOR gate in QCA technology. Transactions on Electrical and Electronic Materials, 21(2) (2020) 198-207. Available:

https://link.springer.com/article/10.1007/s42341-019-00166-y

[40] Dysart, T. J. Modeling of electrostatic QCA wires. IEEE transactions on nanotechnology, 12(4) (2013) 553-560. Available:

https://ieeexplore.ieee.org/document/6497528/

[41] Danehdaran, F., Khosroshahy, M. B., Navi, K., & Bagherzadeh, N. Design and power analysis of new coplanar one-bit full-adder cell in quantum-dot cellular automata. Journal of Low Power Electronics, 14(1) (2018) 38-48.

DOI:10.1166/jolpe.2018.1529

[42] Shin, S. H., Jeon, J. C., & Yoo, K. Y. Wire-crossing technique on quantumdot cellular automata. In NGCIT2013, the 2nd international conference on

44

Journal of Optoelectronical Nanostructures. 2022; 7 (3): 23-45

next generation computer and information technology (2013, September) (52-57). Available:

https://www.semanticscholar.org/paper/Wire-Crossing-Technique-on-Quantum-Dot-Cellular-Shin

[43] Ahmadpour, S. S., & Mosleh, M. A novel fault-tolerant multiplexer in quantum-dot cellular automata technology. The Journal of Supercomputing, 74(9) (2018) 4696-4716. Available:

https://link.springer.com/article/10.1007/s11227-018-2464-9

- [44] Ahmadpour, S. S., & Mosleh, M. New designs of fault-tolerant adders in quantum-dot cellular automata. Nano Communication Networks, 19 (2019) 10-25. Available: <u>https://doi.org/10.1016/j.nancom.2018.11.001</u>

- [45] Mehdizadeh, F., & Alipour-Banaei, H. All optical 1 to 2 decoder based on photonic crystal ring resonator. Journal of Optoelectronical Nanostructures, 2(2) (2017) 1-10.

Available:<u>http://jopn.marvdasht.iau.ir/article\_2419\_91e8a15036a4eb30e9d9f</u> 32002542690.pdf

[46] Ahmadpour, S. S., Mosleh, M., & Asadi, M. A. The development of an efficient 2-to-4 decoder in quantum-dot cellular automata. Iranian Journal of Science and Technology, Transactions of Electrical Engineering, 45(2) (2021) 391-405. Available:

https://link.springer.com/article/10.1007/s40998-020-00375-9

[47] Nayeri, M., Keshavarzian, P., & Nayeri, M. A Novel Design of Penternary Inverter Gate Based on Carbon Nano Tube. Journal of Optoelectronical Nanostructures, 3(1) (2018) 15-26. Available:

http://jopn.marvdasht.iau.ir/article\_2820.html

[48] Karimi Moghadam, D., & Solookinejad, G. Implication of quantum effects on non-linear propagation of electron plasma solitons. Journal of Optoelectronical Nanostructures, 5(3) (2020) 59-70. Available:

http://jopn.marvdasht.iau.ir/article\_4404.html