https://doi.org/10.30495/jce.2023.1996352.1223

## Vol. 14/ No. 54/Winter 2025

**Research Article**

# Low-Power Differential Voltage-Controlled Ring Oscillator Based on Carbon Nanotube Field-Effect Transistor (CNTFET)

Saba Naseri Akbar, MsC 1 🕩

<sup>1</sup>Department of Electrical Engineering, Islamshahr Branch, Islamic Azad University, Tehran, Iran, sabsen1394@gmail.com

#### Correspondence

Saba Naseri Akbar, MsC of Electrical Engineering, Department of Electrical Engineering, Islamshahr Branch, Islamic Azad University, Tehran, Iran Email: sabsen1394@gmail.com

Received: 13 September 2023 Revised: 2 December 2023 Accepted: 20 December 2023

#### Abstract

Due to the better common-mode elimination of power supply voltage and sub-substrate noise, the differential ring oscillator (DRO) performs better than the single-ended ring oscillator (SERO) in both analog and digital integrated circuits. Also, it is easy to achieve high frequency performance with in-phase and quadrature outputs in a differential ring oscillator. For this purpose, in this research, the design and simulation of a three-stage differential voltage controlled circular oscillator (DVCRO) based on carbon nanotube field effect transistor (CNTFET) is presented, whose oscillation frequency can be changed by changing the control voltage of the proposed delay cell structure. A very wide range changed from 45.7 GHz to 110.18 GHz, and at the same time, its power consumption is in the range of 5.17  $\mu$ W to 32.68  $\mu$ W. Based on the results obtained at the supply voltage of 0.9 V, the proposed voltage controlled ring oscillator (VCRO) based on carbon nanotube field effect transistor shows promising characteristics compared to its counterpart based on metal-oxide-semiconductor field effect transistor (MOSFET). Also, it performs exceptionally well compared to other existing oscillators.

**Keywords:** Carbon Nanotube Field Effect Transistor (CNTFET), Power Delay Product (PDP), delay cell, Differential Voltage Controlled Ring Oscillator (DVCRO), Single Ended Ring Oscillator (SERO).

#### Highlights

- Presentation of a new 9-transistor delay cell based on carbon nanotube field effect transistor (CNTFET).

- The changeability of the delay characteristic in the proposed delay cell by changing the control voltage.

- Providing a three-stage differential Voltage Controlled Oscillator (VCO) based on carbon nanotube field effect transistor in the high frequency range and beyond.

- Achieving a wide adjustment range with low power consumption in the proposed voltage-controlled oscillator.

**Citation:** S. Naseri Akbar, "Low-Power Differential Voltage-Controlled Ring Oscillator Based on Carbon Nanotube Field-Effect Transistor (CNTFET)," *Journal of Southern Communication Engineering*, vol. 14, no. 54, pp. 47–68, 2025, doi: 10.30495/jce.2023.1996352.1223, [in Persian].

مقاله پژوهشی

نوسانساز حلقوی تفاضلی کنترلشده با ولتاژ توان پایین مبتنی بر ترانزیستورهای اثر میدان نانولوله کربنی

صبا ناصری اکبر 🕕

۲

گروه برق، ذانشگاه ازاد اسلامی

واحد اسلامشهر، تهران، ایران،

sabsen1394@gmail.com

نویسنده مسئول

نویسنده مسئول

۰

صبا ناصری اکبر، کارشناسی ارشد، دانشگاه آزاد اسلامی

۱۵

مینوبیسنده مسئول

۰

صبا ناصری اکبر، کارشناسی ارشد، دانشگاه آزاد اسلامی

۱۵

مینوبیسنده مسئول

۰

مینوبیسنده مسئول

۱۵

مینوبی تهران، ایران

۱۵

مینوبی تهریوند تا شهریور ۲۰۶۲

۱۵

مینوبی تهریوند: ۲۲ شهریور ۲۰۶۲

۱۵

مینوبی تاریخ دریافت: ۲۲ شهریور ۲۰۶۲

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

۲۰

۱۵

<t

چکیدہ:

به دلیل حذف حالت مشترک بهتر تغذیه و نویز زیر بستر، نوسانساز حلقوی تفاضلی (DRO) عملکرد بهتری نسبت به نوسانساز حلقوی تکسر (SERO) هم در مدارات مجتمع آنالوگ و هم مدارات دیجیتال از خود نشان میدهد. همچنین، دستیابی به عملکرد فرکانس بالا با خروجیهای همفاز و متعامد در نوسانساز حلقوی تفاضلی آسان است. بدین منظور در این پژوهش، طراحی و شبیهسازی یک نوسانساز حلقوی تفاضلی کنترلشده با ولتاژ (DVCRO) سەطبقە بر اساس ترانزيستور اثر ميدان نانولولە كربنى (CNTFET) ارائه می شود که فرکانس نوسان آن را با تغییر ولتاژ کنترل ساختار سلول تأخیر پیشنهادی میتوان در بازه بسیار وسیعی از ۴۵/۷ گیگاهرتز تا ۱۱۰/۱۸ گیگاهرتز تغییر داد و درعین حال توان مصرفی آن در بازه ۵/۱۷ میکرو وات تا ۳۲/۶۸ میکرو وات باشد. بر اساس نتایج به دست آمده در ولتاژ تغذیه ۰/۹ ولت، نوسانساز حلقوی کنترل شده با ولتاژ (VCRO) پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی ویژگیهای امیدوار کنندهای نسبت به همتای مبتنی بر ترانزیستور اثر میدان نيمه هادی-اکسيد-فلز (MOSFET) خود نشان میدهد. همچنين، نسبت به سایر نوسانسازهای موجود عملکرد فوقالعاده خوبی از خود نشان مىدھد.

كليدواژهها: ترانزيستور اثر ميدان نانولوله كربنی (CNTFET)، حاصل ضرب تأخير در توان (PDP)، سلول تأخير، نوسان ساز حلقوی تفاضلی كنترل شده با ولتاژ (DVCRO)، نوسان ساز حلقوی تكسر (SERO).

https://doi.org/10.30495/jce.2023.1996352.1223

#### ۱– مقدمه

با پیشرفت در مدلسازی نیمهرساناها، کوچکسازی اندازه ترانزیستورها، پیشرفتها در فرآیندهای ساخت و با توسعه سریع ابزارهای طراحی کامپیوتری، بازار مدار مجتمع در حال رشد سریع است. امروزه فنّاوری CMOS به دلیل گرایش صنعت به اعمال فنّاوریهای فرآیند استاندارد به پیادهسازی مدارات آنالوگ و دیجیتال در یک تراشه واحد، در طراحی مدارات آنالوگ و در سیستمهای سیگنال مخلوط بر سایر فنّاوریها چیره شده است. با اینکه مدارات دیجیتال زیادی را با توان مصرفی کوچکتر میتوان در سطح کوچکتری جا داد، اما اکثر مدارات آنالوگ موجود به تغییرات زیاد یا حتی طراحی دوباره نیاز دارند. به دلیل ترارسانایی ذاتی کمتر افزارههای CMOS و نیز کاهش بهره به دلیل اثرات کانال کوتاه که در فرآیندهای CMOS زیر میکرون پدیدار میشود، بهینهسازی مدارات آنالوگ با کاهش طول کانال ترانزیستور به چند ده نانومتر بسیار مشکل میشود [۱]. کاهش مقیاس ترانزیستور اثر میدان نیمه هادی-اکسید-فلز<sup>۱</sup> (MOSFET) در حوزه نانو بسیاری از چالشها مانند جریان نشتی گیت، نشتی درین ایجاد شده توسط گیت<sup>۲</sup> (GIDL)، جریان نشتی حالت خاموش، تأخیرها، اتلاف توان، اثرات کانال کوتاه و بسیاری دیگر را آشکار میکند [۲]. این چالشها اجتنابناپذیر هستند، بهطوری که اندازه ترانزیستور مهمترین پارامتری است که باید توسط طراحها در فرآیند کاهش اندازه در نظر گرفته شود. همچنین تکامل مدارهای مجتمع از یک سو و نیاز به کاهش ابعاد ترانزیستورها به منظور افزایش سرعت و کاهش مصرف توان سبب توسعه نسل جدیدی از افزارههای الکترونیکی شده که از آن تحت عنوان نانو افزاره یاد میشود. گر چه امروزه تمایل به استفاده از افزارههای مبتنی بر CMOS رشد روزافزونی داشته است، اما شرایط فیزیکی این دسته از افزارهها محدودیتهایی را در کوچکسازی به وجود میآورند. بهطوری که برای افزارههای با طول گیت پایین تر از ۲۰ نانومتر به ندرت میتوان از CMOS بهره جست؛ بنابراین یکی از ایدههایی که برای استفاده از خواص الکترونیکی نانولولهها وجود دارد، استفاده از آنها به جای سیلیکون در مدارهای الکترونیکی است از خواص الکترونیکی نانولولهها وجود دارد، استفاده از آنها به جای سیلیکون در مدارهای الکترونیکی است (۳). تئوریهای کوانتومی حاکم بر این نوع از مواد سبب شده تا نانولولههای کربنی به عنوان مادهای منانوری نیمههادی مدنظر قرار گیرند [۴].

مسئله اصلی طراحی آنالوگ، موقع سروکار داشتن با فنّاوری نانولوله کربنی، تعیین اندازه ترانزیستورها بهمنظور دستیابی به مشخصات الکتریکی موردنظر است. در هنگام کار با فنّاوری CMOS مرسوم، بهطور کلی متغیرهای آزاد W (عرض کانال گیت) و L (طول کانال گیت) در طراحی مدار نقش دارند؛ اما برای فنآوری ترانزیستور اثر میدان نانولوله کربنی، قطر یک نانولوله ثابت بوده و طول کانال متغیر است. بهمنظور دستیابی به جریانهای بالاتر، ممکن است چندین نانولوله کربنی، قطر یک نانولوله ثابت موده بود و کان کرنال گیت) بوده و طول کانال متغیر است. بهمنظور دستیابی به جریانهای بالاتر، ممکن است چندین نانولوله کربنی، قطر یک نانولوله ثابت شونه بوده و طول کانال متغیر است. بهمنظور دستیابی به جریانهای بالاتر، ممکن است چندین نانولوله (N) بهصورت موازی پیوند شونه بابراین، متغیرهای آزاد L و N هستند. در یک ترانزیستور CMOS، W را میتوان بهطور مداوم تغییر داد. در فنّاوری ترانزیستور اثر میدان نانولوله (I) بهصورت موازی پیوند شونه بابراین، متغیرهای آزاد L و N هستند. در یک ترانزیستور CMOS، W را میتوان بهطور مداوم تغییر داد. در فنّاوری ترانزیستور اثر میدان نانولوله رفاو مداوم تغییر داد. در فنّاوری ترانزیستور اثر میدان میتوان بهطور مداوم تغییر داد. در فنّاوری ترانزیستور می می را می میتوان به مور مداوم تغییر داد. در فنّاوری ترانزیستور اثر میدان نانولوله کربنی، عرض کانال با تعداد نانولولههایی که نواحی سورس و درین را بهطور موازی متصل می کنند ترانزیستور اثر میدان نانولوله کربنی، می مردن دار آن یا تعداد نانولولههایی که نواحی سورس و درین را به مور موازی متصل می کنند ترانزیستور اثر میدان زیر محال، هنگام تجزیه و تحلیل ویژگیهای الکتریکی، این هم ارزی از بین می رود. قطر CND را میتوان بر اساس معادلهی زیر محاسبه کرد [۵]:

$$D_{CNT} = \frac{a \times \sqrt{n_1^2 + n_1 n_2 + n_2^2}}{\pi} \approx 0.0783 \times \sqrt{n_1^2 + n_1 n_2 + n_2^2}$$

(1)

در اینجا nn و249 nm فاصلهی بیناتمی بین اتم کربن و همسایهی آن است. n و n و n اعداد مربوط به بردار کایرالیتی<sup>۳</sup> هستند. ولتاژ آستانه بهعنوان ولتاژی که برای روشن کردن ترانزیستور به آن نیاز است. ولتاژ آستانه یک کانال نانولوله کربنی ذاتی را میتوان در قدم اول، بهصورت نصف شکاف انرژی تقریب زد (که شکاف انرژی با قطر نسبت معکوس دارد). با تعیین قطر نانولوله کربنی، ولتاژ آستانه<sup>†</sup> (th) بهصورت زیر تعریف میشود [۵]:  $V_{th} \approx \frac{E_g}{2e} = \frac{\sqrt{3}}{3} \frac{a V_{\pi}}{e D_{curr}}$

در اینجا D<sub>CNT</sub> قطر نانولوله است [۵]. نوسانساز حلقوی تفاضلی<sup>۵</sup> (DRO) مجتمع سازی شده در فنّاوری CMOS در محصولات متعددی در طول سالیان متمادی استفاده شده است. استفاده از آن در مدارات سرعت بالای کلاک و بازیابی داده<sup>۶</sup> (CDN) مخابرات نوری، نوسانسازهای کنترل شده به طور دیجیتالی و آنالوگ، مقسمهای فرکانسی ترکیبکنندههای<sup>۷</sup> فرکانس بالا، مولدهای کلاک برای مدارات دیجیتال، مبدلهای آنالوگ به دیجیتال<sup>۸</sup> (ADC) و بسیاری از کاربردها توسعه یافته است [۱۰–۶]. پیادهسازی نوسانسازهای حلقوی در فنّاوریهای

- <sup>3</sup> Chirality

- <sup>4</sup> Threshold Voltage

- <sup>5</sup> Differential Ring Oscillator

- <sup>6</sup> Clock and Data Recovery

- <sup>7</sup> Synthesizers

- <sup>8</sup> Analog-to-Digital Converters

<sup>&</sup>lt;sup>1</sup> Metal-Oxide-Semiconductor Field-Effect Transistor

<sup>&</sup>lt;sup>2</sup> Gate-Induced Drain Leakage

نوظهور از قبیل باند فوقالعاده وسیع<sup>۱</sup> (UWB) و تشخیص فرکانس رادیویی<sup>۲</sup> (RFID) و نیز شبکههای حسگر بیسیم<sup>۳</sup> (WSN) و ادوات مخابراتی برد کوتاه مشاهده شده است [۱۱،۱۲]. نوسان ساز حلقوی تفاضلی یک انتخاب طراحی خوب برای طراحان مدار مجتمع، به دلیل استفاده متمادی آن در فنّاوریهای CMOS مختلف، است.

در مرجع [۱۳] یک نوسانساز حلقوی موج میلیمتری بر اساس ترانزیستور اثر میدان نانولوله کربنی<sup>۴</sup> (CNTFET) در فنّاوری ۳۲ نانومتر ارائه شده است که در محدوده فرکانسی ۱۵۰ گیگاهرتز و فراتر کار میکند. اتصال های نانولوله کربنی بین ترانزیستورها نیز در شبیهسازیهای انجامگرفته در این مقاله در نظر گرفته شدهاند، که فرض می شود یک لایه واحد از نانولولههای کربنی فلزی بالستیک به صورت موازی باشد. به خاطر سادگی در طراحی RF، نوسان ساز طراحی شده در مرجع [۱۳] بر اساس وارونگرهای مبتنی ترانزیستور اثر میدان نانولوله کربنی است. وارونگرها با بهره DC برابر ۸۷/۵ دسیبل با طراحی مناسب با تأخیر بدون بارگذاری حدود ۱/۶ پیکوثانیه در نظر گرفته شدهاند که حداقل یک مرتبه بهتر از همان وارونگرها با فنّاوری ۳۲ نانومتر مبتنی بر ماسفت (MOSFET) است. توان مصرفی میانگین این نوسانساز کمتر از ۴۰ میکرو وات با دامنه هارمونیک پایه حدود ۶/۵-دسیبل است. همچنین، بهطور متوسط، عملکرد این نوسانساز ۵ تا ۶ برابر بهتر از طراحیهای مبتنی بر ماسفت است. با توجه به گسترش دستگاههای الکترونیکی قابل حمل و همچنین کاهش مقیاس فنّاوری و محدودیتهای کاهش طول کانال ماسفت، طراحی نوسان ساز حلقوی توان پایین با محدوده فرکانسی وسیع و دارا بودن قابلیت تنظیم فرکانسی برای بسیاری از کاربردها ضروری بوده و تلاشهای زیادی در این زمینه توسط طراحان صورت گرفته است [۲۰-۱۴]. برای پاسخ به چالشهای موجود در مرجع [۱۴] دو نوسانساز حلقوی<sup>۵</sup> (RO) قابل تنظیم مبتنی بر وارونگر FGMOS/CNTFET پیشنهاد شده و از مزایای ترانزیستورهای اثر میدان نانولوله کربنی و تکنیک ترانزیستور MOS با گیت شناور (FGMOS) بهره گرفته است. وارونگرهای پیشنهادی در ساختار این نوسانسازهای حلقوی بهصورت ترکیبی از تکنیک ترانزیستور MOS با گیت شناور و ترانزیستور اثر میدان نانولوله کربنی است که به محدودیت کاهش طول کانال ماسفت غلبه کرده و نوسان سازهای حلقوی فرکانس بالا و توان یایین با قابلیت تنظیم فرکانسی و بدون هرگونه مکانیسم اضافی برای تنظیم فرکانسی معرفی نموده است. در مرجع [۱۵] چندین نوسانساز حلقوی هیبرید مبتنی بر ترانزیستور اثر میدان نانولوله کربنی و ماسفت معرفی شده است. طبق بررسیهای انجامشده بر روی یک نوسانساز حلقوی سهطبقه، در مرجع [۱۵] گزارششده که محل قرارگیری وارونگرهای مبتنی بر ترانزیستور اثر میدان نانولوله کربنی و MOSFET می تواند تأثیر بسزایی بر روی فرکانس نوسان نوسانساز حلقوی سهطبقه داشته باشد و نوسانسازهایی با فرکانس نوسان در محدوده چند گیگاهرتز معرفی شدهاند. در مرجع [۱۶] چندین نوسانساز حلقوی ۷ طبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی دو گیتی (DG-CNTFET) ارائهشده که در آنها از ترانزیستورهای اثر میدان نانولوله کربنی دو گیتی برای افزودن ویژگی تنظیم فرکانسی به مدار نوسانساز استفاده شده است. در مرجع [۱۷]، نوسانساز حلقوی قابل تنظیم با استفاده از ترانزیستور اثر میدان نانونوار گرافینی<sup>۶</sup> (GNRFET) ارائه شده است که سلول تأخیر در این نوسانساز حلقوی مبتنی بر گیت NAND و Inverter است. شایان ذکر است که گرافین شکل باز شدهای از نانولوله کربنی است. حاصل ضرب تأخیر در توان (PDP) نوسانسازهای پیشنهادی در مرجع [۱۷] در مقایسه با تکنیکهای پیشرفته و بهروز فوقالعاده پایین است که این طرح را برای کاربردهای توان پایین و فرکانسهای در محدوده موج میلیمتری بسیار مناسب میسازد. در مرجع [۱۸]، نوسان ساز حلقوی قابل تنظیم با استفاده از ترانزیستور اثر میدان نانولوله کربنی معرفی شده است که در آن سلول تأخیر مبتنی بر گیت NAND سه ترانزیستوری بوده و مدارهای نوسانساز کنترلشده با ولتاژ سه، پنج و هفت طبقهای بر اساس این سلول تأخیر طراحی شدهاند. بر اساس نتایج حاصله حاصل ضرب تأخیر در توان نوسان سازهای پیشنهادی در مرجع [۱۸] در مقایسه با تکنیکهای پیشرفته و بهروز فوقالعاده پایین بوده و برای کاربردهای توان پایین و فرکانس بسبالا بسیار مناسب هستند. در مرجع [۱۹]، نوسانساز حلقوی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با قابلیت پیکربندی مجدد و تنظیم فرکانسی ارائه شده است که در آن سلول تأخیر پیشنهادی در آن مبتنی بر گیت NAND و NOR سوئیچ شده است که در هر لحظه از زمان

<sup>&</sup>lt;sup>1</sup> Ultra Wideband

<sup>&</sup>lt;sup>2</sup> Radio Frequency Identification

<sup>&</sup>lt;sup>3</sup> Wireless Sensor Networks

<sup>&</sup>lt;sup>4</sup> Carbon NanoTube FET 5 Ring Oscillator

<sup>&</sup>lt;sup>6</sup> Graphene Nano-Ribbon Field-Effect Transistor

فقط یکی از این سلولها با استفاده از سوئیچهای در نظر گرفته شده فعال می شوند تا عمل پیکربندی مجدد در ساختار نوسان ساز رخ دهد. همچنین با اعمال یک سیگنال کنترلی به یکی از پایانه های ورودی گیت NAND و NON مشخصه تأخیر این سلول ها تغییر کرده و بدین نحو عمل تنظیم فرکانسی در نوسان ساز پیشنهادی صورت می گیرد. این طرح برای کاربردهای توان پایین، چند استانداردی و طیف فرکانسی در محدوده های فرکانس بالا<sup>۱</sup> (HF) و فرکانس خیلی بالا<sup>۲</sup> (VHF) بسیار مناسب است. در مرجع [۲۰]، نوسان ساز حلقوی کنترل شده با ولتاژ<sup>۳</sup> (VCRO) با استفاده از ترانزیستور اثر میدان نانو نوار گرافینی ارائه شده که در آن سلول تأخیر استفاده شده در ساختار نوسان ساز مبتنی بر گیت MAND دو ترانزیستوری مبتنی بر تکنیک GDI<sup>4</sup> است. نوسان ساز کنترل شده با ولتاژ سه طبقه در مرجع [۲۱] با شش عدد ترانزیستور تحقق یافته است که این طرح را برای کاربردهای توان پایین مناسب ساخته و فرکانس های در محدوده فرکانس بالا و فراتر از آن تا محدوده موج میلی متری<sup>6</sup> (EHF) را پوشش

همان طور که در بالا اشاره شد، گرایش به کاربردهای توان پایین و افزایش مجتمعسازی به ساختارهای جدید برای مدارات نیاز دارد. به این دلیل در این پژوهش قصد داریم تا یک نوسان ساز حلقوی تفاضلی جدید را با استفاده از ترانزیستور اثر میدان نانولوله کربنی معرفی نموده و مزیت های طرح پیشنهادی را در افزایش و بهبود پارامترهای اصلی یک نوسان ساز نشان دهیم. دید کلی از این پژوهش به صورت زیر است. در بخش دوم نوسان ساز حلقوی تفاضلی کنترل شده با ولتاژ جدید بر اساس ترانزیستورهای نانولوله کربنی ارائه می شود. در بخش سوم نتایج شبیه سازی ارائه شده و در بخش چهارم، نتیجه گیری ارائه خواهد شد.

## ۲- طرح پیشنهادی

یک نوسانساز حلقوی با به کارگیری تعداد زوج یا فردی از تقویت کننده وارونگر حلقه باز یا سلولهای تأخیر (طبقات تأخیر) که در یک حلقه فیدبک مثبت وصل شدهاند ساخته میشود (شکل ۱). در طی عملکرد اگر یکی از گرههای نوسانساز حلقوی تحریک شود، پالس از طریق تمامی سلولها انتشار یافته و سرانجام پلاریته گره تحریک شده اصلی را معکوس می کند. لازم به ذکر است معیار بارکهاوزن<sup>6</sup> برای پایداری نوسان لازم است اما برای شرایط راهاندازی کافی نیست. برای تضمین هر نوعی از راهاندازی نوسانساز در آغاز، بهره حلقه باز نوسانساز باید همیشه بزرگتر از واحد باشد. هنگامی که این شرط برقرار شد، ممکن به ولتاژ تغذیه ضربه بخورد. این پدیدهها در هر نوسانساز عملی واضح هستند [۲۲].

شکل ۱: یک نوسان ساز حلقوی تحقق یافته با استفاده از سه وارونگر دیجیتال Figure 1. A ring oscillator realized using three digital inverters

در نوسانساز حلقوی، سیگنال انتشار دو مرتبه از طریق زنجیرهای از N سلول تأخیر، برای تأخیر کل 2Nt<sub>p</sub>، بهمنظور کامل کردن یک پریود (T<sub>osc</sub>) عبور میکند؛ t<sub>p</sub> زمان انتشار یک سلول تأخیر واحد است. فرکانس (f) این نوسانساز معیاری از زمان سیر از طریق حلقه بوده و میتواند به صورت زیر استنتاج شود: (۳)

<sup>&</sup>lt;sup>1</sup> High Frequency

<sup>&</sup>lt;sup>2</sup> Very High Frequency

<sup>&</sup>lt;sup>3</sup> Voltage Controlled Ring Oscillator

<sup>&</sup>lt;sup>4</sup> Gate Diffusion Input

<sup>&</sup>lt;sup>5</sup> Extremely High Frequency (Millimeter Wave)

<sup>6</sup> Barkhausen

معمولاً، tp یک نوسانساز حلقوی با حاصلضرب بار مقاومتی (RLoad) و خازن کل (Ctotal) بار و خازنهای پارازیتی ادوات اکتیو در یک مدار سلول تأخیر با یک ضریب ثابت محاسبه می شود. علاوه بر این، RLoad را می توان با سوئینگ ولتاژ خروجی نسبت به جریان (بایاس) بار کل در هر سلول تأخیر نمایش داد [۲۲].

سلولهای تأخیر نوسانساز حلقوی میتوانند تکسر یا تفاضلی باشند. نوسانساز حلقوی تکسر<sup>۲</sup> (SERO) زنجیرهای از وارونگرهای تشکیلشده از یک ترانزیستور NMOS و PMOS است و تعداد سلولهای تأخیر باید فرد باشد. سلولهای تأخیر نوسانساز حلقوی تفاضلی می تواند فرد یا حتی تعداد زوجی باشد و با به کارگیری یک بار (المان های فعال و غیرفعال) با یک زوج ورودی زوجهای تفاضلی NMOS یا وارونگر یوش یول<sup>۳</sup> ساخته شود. زمان انتشار در این نوع از سلول با بار در هر گره و جریان گذرنده از بار که ممکن است یک مقاومت برای فرکانس ثابت یا ترانزیستورهای PMOS باشد تنظیم شود. هر دو توپولوژی تک سر و تفاضلی می توانند در طراحی نوسانسازهای کنترلشده با ولتاژ CMOS کاملاً مجتمع استفاده شوند. بر اساس خروجیهای ساختارهای سلول تأخیر آن، نوسانساز حلقوی تفاضلی میتواند به سه گروه تقسیمبندی شود: اشباعشده، اشباعنشده و غیر اشباعشده [۶]. طبقه خروجی نوسان ساز حلقوی تک سر همیشه اشباعنشده است. به این دلیل، نوسان ساز حلقوی تک سر عملکرد نویز فاز بهتری برای تعداد برابری از طبقات ارائه می کند در حالی که توان مصرفی خیلی پایین است و عملکرد نویز حرارتی فوقالعادهای از خود نشان می دهد [۱۳]. به دلیل حذف مد مشترک بهتر تغذیه و نویز زیر بستر، نوسانساز حلقوی تفاضلی عملکرد بهتری نسبت به نوسانساز حلقوی تکسر هم در مدارات مجتمع آنالوگ و هم مدارات دیجیتال از خود نشان میدهد [۸]. علاوه بر این، دستیابی به عملکرد فرکانس بالا با خروجیهای همفاز و متعامد در نوسان ساز حلقوی تفاضلی آسان است [۹]. نوسانساز حلقوی در شکل ۱ بر اساس ساختار مبتنی بر وارونگر<sup>۴</sup> است که شامل سه وارونگر سری در یک حلقه بسته است. حداقل تعداد سه وارونگر انتخاب می شود تا به بیشترین فرکانس نوسان دستیابیم. فرکانس نوسان این نوسانساز به صورت زیر تعیین می شود [۱۳]:

$$f_{osc} = \frac{1}{2\pi N \left(\tau_{PHL} + \tau_{PLH}\right)} \tag{(f)}$$

که در اینجا N تعداد گیتهای وارونگر در حلقه، ۲<sub>PHL</sub> تأخیر High به ۲<sub>PLH</sub> ،Low تأخیر Low به High هر وارونگر دارای تمامی بارهای پارازیتی در گرههای ورودی و خروجی است. ساختار اتصال بین سه وارونگر مابین سه وارونگر نقش مهمی در تعریف تأخیر کل هر وضعیت و در نتیجه ماکزیمم فرکانس نوسان دستیافتنی بازی میکند.

<sup>1</sup> Swing

<sup>2</sup> Single-Ended RO

1

- <sup>3</sup> Push-Pull

- <sup>4</sup> Inverter

/**x**

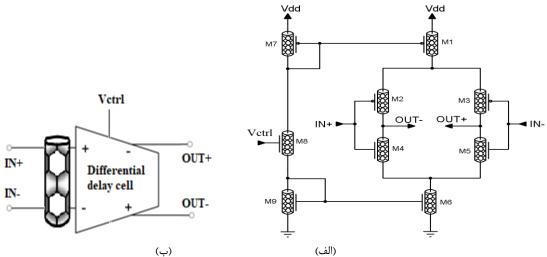

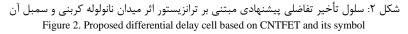

در ادامه یک نوسانساز سهطبقه تفاضلی را پیشنهاد می کنیم. سلول تأخیر پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی برای استفاده در ساختار نوسانساز پیشنهادی در شکل ۲ نشان داده شده است که قابلیت تنظیم تأخیر آن توسط ولتاژ کنترلی V<sub>ctr</sub> وجود دارد. ترانزیستور اثر میدان نانولوله کربنی مورداستفاده در اینجا ترانزیستور اثر میدان نانولوله کربنی شبه ماسفت<sup>۱</sup> است. این امر به دلیل پارامترهای برتر افزاره و راحتی ساخت ترانزیستور اثر میدان نانولوله کربنی هاسفت در مقایسه با FETهای با سد شاتکی کنترل شده است که ترانزیستور اثر میدان نانولوله کربنی شبه ماسفت در در فرکانس بالاتر مناسب می سازد. در شکل ۳ ساختار نوسانساز تفاضلی کنترل شده با ولتاژ پیشنهادی سه ماسفت ایر ترانزیستور اثر میدان نانولوله کربنی نشان داده شده که در آن از سلول تأخیر پیشنهادی شکل ۲ استفاده شده است.

شکل ۳: بلوک دیاگرام نوسانساز حلقوی تفاضلی پیشنهادی سهطبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی Figure 3. Block diagram of proposed three-stage DRO based on CNTFET

### ۳- نتایج شبیهسازی

در این بخش عملکرد نوسانساز حلقوی تفاضلی کنترلشده با ولتاژ سهطبقه پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با استفاده از فنّاوری ۳۲ نانومتر و ولتاژ تغذیه ۰/۹ ولت و با آزمایشهای مختلف موردبررسی قرار خواهد گرفت. سپس برای بررسی بیشتر با ماسفت نیز پیادهسازی شده و عملکرد دو فنّاوری ماسفت و ترانزیستور اثر میدان نانولوله کربنی در ساختار نوسانساز پیشنهادی مورد ارزیابی قرار خواهد گرفت.

# ۳-۱-شبیه سازی طرح پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی

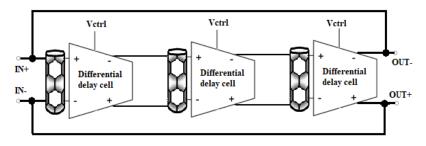

برای عملکرد مناسب سلول تأخیر نشان دادهشده در شکل ۲ تعداد نانولولههای کربنی استفادهشده در ترانزیستورهای M6، M1 و M7 تا M9 را برابر ۳ در نظر می گیریم. و M7 تا M9 را برابر ۳ در نظر می گیریم. برای سایر ترانزیستورها تعداد نانولولههای کربنی زیر گیت را برابر ۱ در نظر می گیریم. در شکل ۴ نتیجه شبیهسازی تابع انتقال ولتاژ سلول تأخیر مبتنی بر ترانزیستور اثر میدان نانولوله کربنی و ماسفت با تغییر ولتاژ تغذیه نشان داده شده است. با توجه به شکل ۴ عملکرد مناسب سلول تأخیر پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی نسبت به نمونه ماسفت واضح و آشکار است.

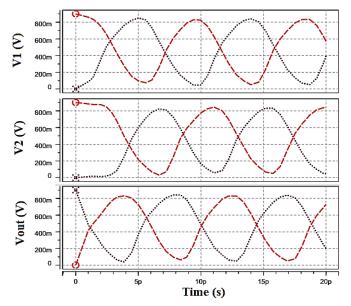

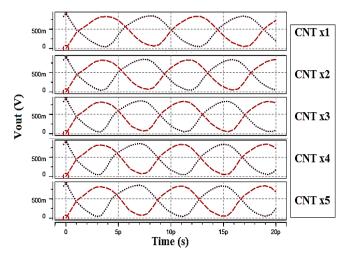

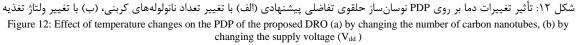

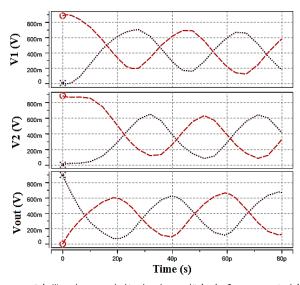

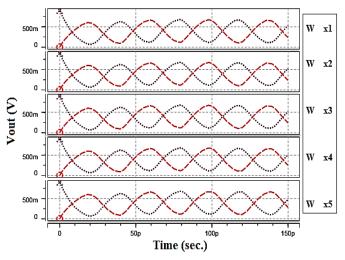

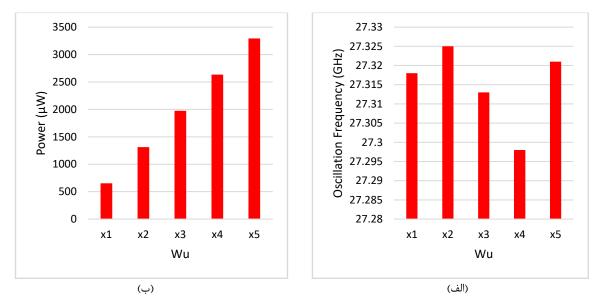

در شکل ۵ ولتاژ گرههای داخلی نوسانساز تفاضلی پیشنهادی ۳ طبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی نشان داده شده است. در این شکل ۷۱، ۷2 و vout به ترتیب به ولتاژ خروجی تفاضلی طبقات اول، دوم و سوم اشاره می کند. در شکل ۶ نتیجه شبیهسازی نوسانساز تفاضلی پیشنهادی ۳ طبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با افزایش ۱ تا ۵ برابری تعداد نانولولههای کربنی در زیر گیت هر ترانزیستور و با طول گیت ۳۲ نانومتر و ولتاژ کنترل ۷۵ – Vctrl نشان داده شده است. افزایش تعداد نانولولههای کربنی در زیر گیت هر ترانزیستور و با طول گیت ۲۲ نانومتر و ولتاژ کنترل ۷.90 – Vctrl است. افزایش تعداد نانولولههای کربنی، به دلیل افزایش قابلیت درایو نمودن وارونگر سوم و کاهش مقاومت اتصال، فرکانس نوسان را افزایش خواهد داد؛ اما در نهایت، افزایش تعداد نانولولههای کربنی خازنهای پارازیتی بیشتری را ایجاد خواهد نمود و در نتیجه عملکرد نوسانساز کاهش خواهد یافت.

<sup>&</sup>lt;sup>1</sup> MOSFET-like

شکل ۴: منحنی مشخصه انتقال ولتاژ سلول تأخیر پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی و ماسفت به ازای ولتاژهای تغذیه مختلف Figure 4. Voltage transfer characteristic curve of the proposed delay cell based on CNTFET and MOSFET for different supply voltages

شکل ۵: ولتاژ خروجی هر یک از طبقات نوسانساز تفاضلی پیشنهادی ۳ طبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی Figure 5. The output voltage of each stage of the proposed 3-stage DRO based on CNTFET

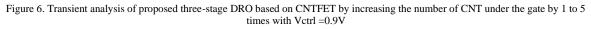

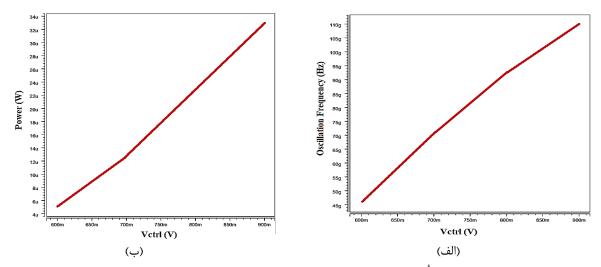

منحنیهای فرکانس نوسان و توان مصرفی این آزمایش در شکل ۷ نمایش داده شده است. با توجه به این شکل مشخص می شود که با افزایش ۱ تا ۵ برابری تعداد نانولولههای کربنی در نوسان ساز تفاضلی پیشنهادی فرکانس نوسان در بازه ۱۱۰ گیگاهرتز تا ۱۲۰ گیگاهرتز تغییر خواهد کرد. همچنین با افزایش تعداد نانولوله کربنی فرکانس نوسان افزایش یافته و توان مصرفی در بازه ۳۳/۳ میکرو وات تا ۱۶۲ میکرو وات تغییر خواهد نمود.

شکل ۶: آنالیز زمانی نوسانساز حلقوی تفاضلی پیشنهادی سهطبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با یک تا پنج برابر کردن تعداد نانولولههای کربنی در زیر گیت با ولتاژ کنترلی برابر ۰/۹ ولت

شکل ۲: (الف) فرکانس نوسان، (ب) توان مصرفی میانگین نوسانساز حلقوی تفاضلی پیشنهادی سهطبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با یک تا ۵ برابر کردن نانولولههای زیر گیت با ولتاژ کنترلی برابر ۰/۹ ولت

Figure 7. (a) Frequency of oscillation, (b) average power consumption of the proposed three-stage DRO based on CNTFET by multiplying the number of CNTs under the gate by 1 to 5 with Vctrl =0.9V

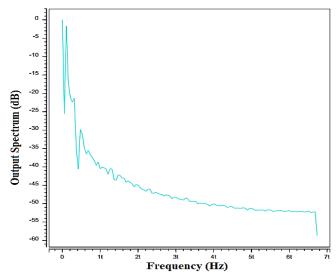

در شکل ۸ طیف خروجی برای نوسانساز تفاضلی پیشنهادی سهطبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با طول گیت ۳۲ نانومتر و تعداد یک برابری نانولوله کربنی در زیر گیت نشان داده شده است که بر اساس آنالیز فوریه در HSPICE بوده است. بر اساس این شکل دامنه هارمونیک اصلی ۱/۷۶دسیبل و THD برابر ۳/۵۶۷ درصد است. برای تعداد نانولولههای کربنی بیشتر نتایج به صورت خلاصه در جدول ۱ نشان داده شده است. ضریب شایستگی وابسته به خطینگی (FoM<sub>THD</sub>) با عنوان معیار شایستگی هارمونیک در جدول ۱ به صورت زیر محاسبه می شود که در آن FHM دامنه هارمونیک اصلی، f<sub>osc</sub> فرکانس نوسان، THD اعوجاج هارمونیک کلی و P<sub>avg</sub> توان مصرفی میانگین است [۱۳].

$$FoM_{THD} = \frac{FHM \times f_{osc.}}{THD \times P_{avg.}}$$

( $\Delta$ )

شکل ۸: طیف خروجی برای نوسانساز حلقوی تفاضلی پیشنهادی ۳ طبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با طول گیت ۳۲ نانومتر و با تعداد ۱ برابری نانولوله کربنی زیر گیت

Figure 8. The output spectrum for the proposed 3-stage DRO based on CNTFET with a gate length of 32 nm and with 1 times the number of CNTs under the gate

جدول ۱: فرکانس نوسان، دامنه هارمونیک اصلی، اعوجاج هارمونیک کل، توان مصرفی میانگین و FoM<sub>THD</sub> برای تعداد مختلف نانولولههای کربنی زیر گیت و طول گیت ۲۳ نانومتر برای نوسانساز تفاضلی پیشنهادی سهطبقه

Table 1. Oscillation frequency, fundamental harmonic amplitude, total harmonic distortion, average power consumption and FoM<sub>THD</sub> for different number of CNTs under the gate and 32 nm gate length for the proposed three-stage DRO

| معیار شایستگی | توان مصرفي ميانگين | اعوجاج هارمونیک کل | دامنه هارمونیک پایه | فركانس نوسان | تعداد نانولولەھاي |

|---------------|--------------------|--------------------|---------------------|--------------|-------------------|

| هارمونيک      | (میکرو وات)        | (درصد)             | (دسىبل)             | (گيگاهرتز)   | کربنی در زیر گیت  |

| • /VV         | 37/7/              | ٣/٥٦٧              | -1/V٦               | 11./18       | ×١                |

| •/0٦          | 70/12              | ٢/٥٦٦              | $-1/\Lambda r$      | 117/29       | ×Y                |

| • /٣٣         | 97/01              | ۲/۹٥٣              | -1/9.               | 111/90       | × <b>٣</b>        |

| •/٦٩          | 129/12             | 1/•٣٦              | -1/•V               | 119/37       | ×٤                |

| • / ٤ ٥       | 177/72             | 1/70/              | -۲/۱۳               | 119/08       | ×o                |

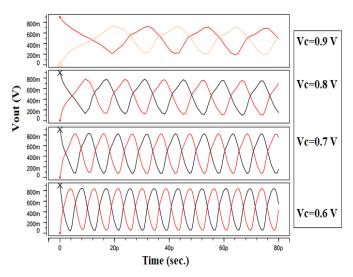

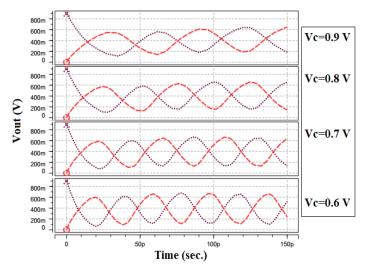

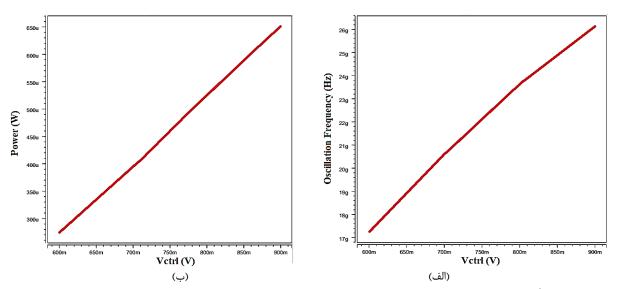

در شکل ۹ آنالیز زمانی نوسانساز تفاضلی پیشنهادی سهطبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با تغییر ولتاژ کنترل Vctrl در بازه ۱/۶ ولت تا ۱/۹ ولت نشان داده شده است. در نمودارهای شکل ۱۰ تأثیر تغییر ولتاژ کنترل Vctrl بر روی فرکانس نوسان و توان مصرفی نوسانساز پیشنهادی نشان داده شده است. با توجه به این شکل با تغییر ولتاژ کنترلی Vctrl در بازه ۶/۶ ولت تا ۲/۹ ولت فرکانس نوسان و توان مصرفی میانگین به ترتیب در بازه ۴۵/۷۰ گیگاهرتز تا ۱۱۰/۱۱ گیگاهرتز و در بازه ۷/۱۷ میکرو وات تا ۲/۶۸ میکرو وات تغییر میکند.

شکل ۹: آنالیز زمانی نوسانساز حلقوی تفاضلی پیشنهادی سه طبقه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با تغییر ولتاژ کنترل Figure 9. Transient analysis of the proposed three-stage DRO based on CNTFET with control voltage change

شکل ۱۰: تأثیر تغییرات ولتاژ کنترلی Vctrl بر روی (الف) فرکانس نوسان، (ب) توان مصرفی Figure 10. Effect of control voltage changes (Vctrl ) on (a) oscillation frequency, (b) power consumption

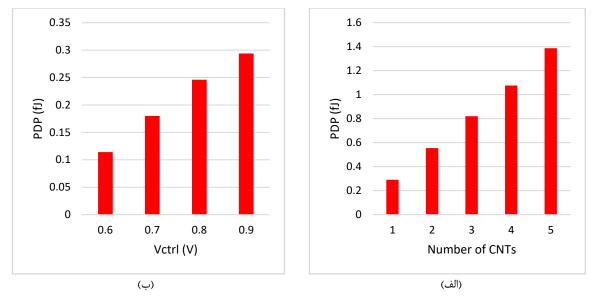

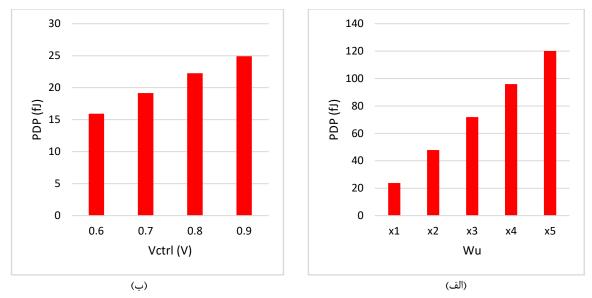

برای مقایسه بهتر، PDP بهعنوان معیار انرژی در نظر گرفته شده است که بهصورت حاصل ضرب توان میانگین (Pavg) و تأخیر گیت (t<sub>d</sub>) تعریف می شود. برای کاربردهای توان پایین، مقدار PDP باید به حداقل رسانده شود. برای یک نوسان ساز حلقوی، این معیار به صورت زیر تعیین می شود [۲۰]:

(6)

$$PDP = P_{avg.} \times t_{d} = \frac{P_{avg.}}{2 \times N \times f_{osc.}}$$

که در اینجا N تعداد طبقات و f<sub>osc</sub> فرکانس نوسان است.

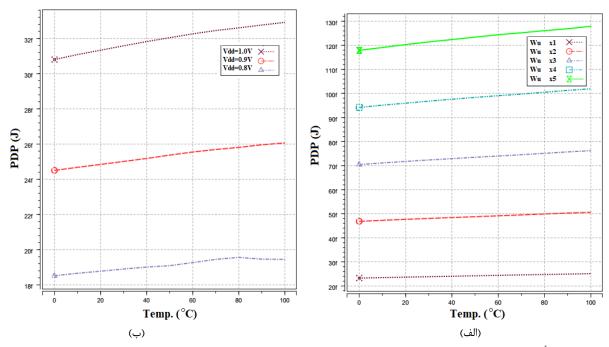

در شکل ۱۱ تأثیر تغییرات تعداد نانولوله کربنی و تغییر ولتاژ کنترل Vctrl بر روی مقدار PDP نشان داده شده است. با توجه به شکل ۱۱–الف مشخص است که با افزایش تعداد نانولولههای کربنی وضعیت معیار PDP بدتر می شود و کمترین مقدار PDP به تعداد نانولوله کربنی برابر یک تعلق دارد. همچنین با توجه به شکل ۱۱(ب) مقدار PDP برای ولتاژ کنترل ۰/۶ ولت کمترین مقدار است. برای ولتاژ کنترل ۰/۹ ولت نیز همچنان مقدار PDP عدد کوچکی است.

شکل ۱۱: تغییرات PDP نوسانساز حلقوی تفاضلی پیشنهادی برحسب (الف) تعداد نانولولههای کربنی، (ب) ولتاژ کنترل Vctrl Figure 11: PDP variations of the proposed DRO in terms of (a) number of carbon nanotubes, (b) control voltage (Vctrl)

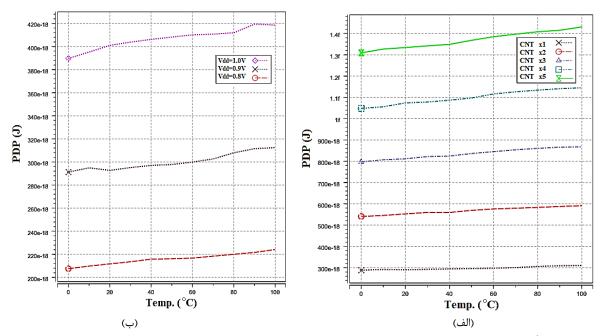

در ادامه تأثیر تغییرات دما بر روی عملکرد نوسانساز سهطبقه تفاضلی پیشنهادی موردبررسی قرار گرفته است. در شکل ۱۲ تأثیر تغییرات دما بر روی PDP نوسانساز پیشنهادی با در نظر گرفتن تعداد نانولولههای کربنی مختلف (افزایش ۱ تا ۵ برابری تعداد نانولولههای کربنی) و ولتاژهای تغذیه مختلف (۸/۰ ولت تا ۱ ولت با گامهای ۰/۱ ولت) نشان داده شده است. نتایج بیانگر آن است که PDP طرح پیشنهادی نسبت به تغییرات دما مقاوم است.

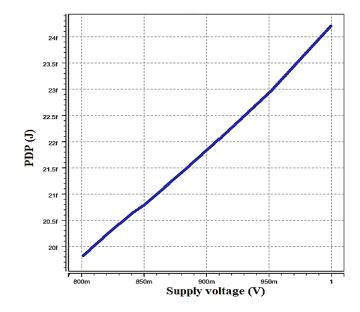

در شکل ۱۳ تأثیر تغییرات ولتاژ تغذیه بر روی PDP نوسانساز پیشنهادی نشان داده شده است. با توجه به شکل ۱۳ با تغییر ولتاژ تغذیه در بازه ۸/۸ ولت تا ۱ ولت مقدار PDP از ۲۱۳ آتو ژول تا ۲۶۳ آتو ژول تغییر میکند. تغییر ۲۵ درصدی در ولتاژ تغذیه به تغییر ۲۳/۴۷ درصدی در مقدار PDP میشود و همچنان مقدار PDP بسیار پایین است.

شکل ۱۳: تأثیر تغییرات ولتاژ تغذیه بر روی PDP نوسانساز حلقوی تفاضلی پیشنهادی Figure 13: Effect of supply voltage changes on the PDP of the proposed DRO

## ۲-۳- شبیه سازی طرح پیشنهادی با ماسفت

در ادامه نوسانساز سهطبقه تفاضلی (پیشنهادشده در شکل ۳) را، که مبتنی بر ترانزیستور اثر میدان نانولوله کربنی بود، با استفاده از ترانزیستورهای ماسفت موردبررسی قرار میدهیم. برای عملکرد مناسب سلول تأخیر عرض ترانزیستورهای M1 و M7 را برابر ۲/۷ میکرومتر، عرض ترانزیستورهای M2، M4 و M9 را برابر ۰/۹ میکرومتر و عرض ترانزیستورهای M3، M5 و M8 را برابر ۰/۳ میکرومتر در نظر می گیریم. طول کانال تمامی ترانزیستورها ۳۲ نانومتر در نظر گرفته شده است.

در شکل ۱۴ ولتاژ گرههای داخلی نوسانساز تفاضلی پیشنهادی ۳ طبقه مبتنی بر ماسفت نشان داده شده است. در این شکل ۷۱، ۷۷ و Vout به ترتیب به ولتاژ خروجی تفاضلی طبقات اول، دوم و سوم اشاره میکند. در شکل ۱۵ نتیجه شبیهسازی نوسانساز تفاضلی پیشنهادی ۳ طبقه مبتنی بر ماسفت با افزایش ۱ تا ۵ برابری عرض هر ترانزیستور و با طول گیت ۳۲ نانومتر و ولتاژ کنترل Vet او U2:0 نشان داده شده است. با توجه به شبیهسازی مشابهی که با استفاده از ترانزیستور اثر میدان نانولوله کربنی با افزایش یک تا ۵ برابری تعداد نانولولههای کربنی در نوسانساز تفاضلی پیشنهادی انجام دادیم متوجه میشویم که تغییر عرض ترانزیستور در نوسانساز تفاضلی مبتنی بر ماسفت تأثیر قابل توجهی بر روی فرکانس نوسان ندارد.

شکل ۱۴: ولتاژ خروجی هر یک از طبقات نوسانساز تفاضلی پیشنهادی ۳ طبقه مبتنی بر ماسفت Figure 14. The output voltage of each stage of the proposed 3-stage DRO based on MOSFET

شکل ۱۵: آنالیز زمانی نوسانساز حلقوی تفاضلی پیشنهادی سهطبقه مبتنی بر ماسفت با افزایش یک تا ۵ برابری عرض ترانزیستورها با ولتاژ کنترلی برابر ۰/۹ ولت

Figure 15. Transient analysis of the proposed three-stage DRO based on MOSFET with one to five times the width of the transistors with Vctrl = 0.9V

منحنیهای فرکانس نوسان و توان مصرفی این آزمایش در شکل ۱۶ نشان داده شدهاند. با توجه به این شکل مشخص می شود که با افزایش یک تا ۵ برابری عرض ترانزیستورها در نوسانساز تفاضلی مبتنی بر ماسفت فرکانس نوسان در بازه ۲۷/۲۹ گیگاهرتز تا ۲۷/۳۲ گیگاهرتز تغییر خواهد کرد. در اینجا چون تأخیر بزرگی با توجه به تغییر اندازه ترانزیستورها ایجاد نمی شود به تغییرات زیاد در فرکانس نوسان منجر نمی شود. همچنین توان مصرفی در بازه ۶۵۱/۱۲ میکرو وات تا ۳/۲۹ میلی وات تغییر خواهد نمود. در حالی که در نوسانساز تفاضلی پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با افزایش یک تا ۵ برابری تعداد نانولولههای کربنی فرکانس نوسان در بازه ۱۱۰ گیگاهرتز تا ۱۲۰ گیگاهرتز تغییر کرد. همچنین توان مصرفی در بازه ۳/۲۹ میکرو وات تا ۱۶۲ میکرو وات تغییر کرد.

شکل ۱۶: (الف) فرکانس نوسان، (ب) توان مصرفی میانگین نوسانساز حلقوی تفاضلی پیشنهادی سهطبقه مبتنی بر ماسفت با یک تا ۵ برابر کردن عرض ترانزیستورها با ولتاژ کنترلی برابر ۲۹۰ ولت

Figure 16. (a) Oscillation frequency, (b) average power consumption of the proposed MOSFET-based three-stage DRO with one to five times the width of the transistors with Vctrl =0.9V

در شکل ۱۷ طیف خروجی برای نوسانساز تفاضلی سهطبقه مبتنی بر ماسفت با طول گیت ۳۲ نانومتر و تعداد یک برابری عرض ترانزیستورها نشان داده شده است که بر اساس آنالیز فوریه در HSPICE بوده است. بر اساس این شکل دامنه هارمونیک اصلی ۲/۴۳- دسیبل و THD برابر ۲/۲۵ درصد است. برای عرض ترانزیستور چند برابر شده نتایج بهصورت خلاصه در جدول ۲ نشان داده شده است.

شکل ۱۷: طیف خروجی برای نوسانساز حلقوی تفاضلی ۳ طبقه مبتنی بر ماسفت با طول گیت ۳۲ نانومتر و با تعداد ۱ برابری عرض ترانزیستورها Figure 17. Output spectrum for MOSFET-based 3-stage DRO with gate length of 32 nm and number of transistors width 1 times

جدول ۲: فرکانس نوسان، دامنه هارمونیک اصلی، اعوجاج هارمونیک کل، توان مصرفی میانگین و FOM برای عرضهای مختلف ترانزیستورها و طول

گیت ۳۲ نانومتر برای نوسانساز حلقوی تفاضلی سهطبقه مبتنی بر ماسفت

Table 2. Oscillation frequency, fundamental harmonic amplitude, total harmonic distortion, average power consumption and FOM for different transistor widths and 32 nm gate length for MOSFET-based three-satge DRO

| معيار شايستگى | توان مصرفي ميانگين | اعوجاج هارمونيك | دامنه هارمونیک پایه | فركانس نوسان | افزایش عرض |

|---------------|--------------------|-----------------|---------------------|--------------|------------|

| هارمونيک      | (میکرو وات)        | کل (درصد)       | (دسىبل)             | (گيگاهرتز)   | ترانزيستور |

| •/•1٤         | 201/18             | ۲/۲٥            | -۲/٤٣               | ۲۷/۳۱۸       | ×١         |

| •/••V         | 1817/2             | ۲/۲۳            | -7/23               | ۲۷/۳۲٥       | ×Y         |

| •/••£         | 1927/1             | ٢/١٩            | -7/27               | 20/212       | × <b>r</b> |

| •/••٣٦        | 2222/2             | ۲/۱٥            | -٢//٤٢              | VV/YAA       | ×٤         |

| •/••۲٩        | WT97/9             | ۲/۱۲            | -7/27               | 20/221       | ×٥         |

در شکل ۱۸ آنالیز زمانی نوسانساز تفاضلی سهطبقه مبتنی بر ماسفت با تغییر ولتاژ کنترل Vctrl در بازه ۶/۰ ولت تا ۹/۰ ولت نشان داده شده است. در نمودارهای شکل ۱۹ تأثیر تغییر ولتاژ کنترل Vctrl بر روی فرکانس نوسان و توان مصرفی نوسانساز فرکانس نوسان و توان مصرفی میانگین به ترتیب در بازه ۱۷/۲۵ گیگاهرتز تا ۲۶/۱۴ گیگاهرتز و در بازه ۶/۰ ولت تا ۹/۰ ولت فرکانس نوسان و توان مصرفی میانگین به ترتیب در بازه ۱۷/۲۵ گیگاهرتز تا ۲۶/۱۴ گیگاهرتز و در بازه ۶/۰ ولت تا ۹/۰ ولت ولکانس نوسان و توان مصرفی میانگین به ترتیب در بازه ۱۷/۲۵ گیگاهرتز تا ۲۶/۱۴ گیگاهرتز و در بازه ۶/۰ ولت تا ۹/۰ ولت تا ۱۹/۱۴۹ میکرو وات تغییر می کند. برای نوسانساز تفاضلی پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با تغییر ولتاژ کنترلی Vctrl در بازه ۶/۰ ولت تا ۹/۰ ولت فرکانس نوسان و توان مصرفی میانگین به ترتیب در بازه ۲۵/۷۰ گیگاهرتز تا ۱۱۰/۱۸ گیگاهرتز و در بازه ۱۰/۱۷ میکرو وات تا ۳۲/۶۸ میکرو وات تغییر نمود. با توجه به این نتایج مشاهده میشود که در نوسانساز تفاضلی پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با تغییر ولتاژ کنترل می توان حدود ۲/۱۴ برابر فرکانس نوسان را تغییر داد در حالی که در نوسانساز مبتنی بر ماسفت حدود ۱۸ برابر می توان در میدان را تنظیم کرد؛ بنابراین می توان نتیجه گرفت که نوسانساز پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی قابلیت تنظیم بالایی از خود نشان می دهد و از لحاظ توان مصرفی نسبت به نوسانساز مبتنی بر ماسفت حدود ۱۸ برابر می توان کمتر مصرف می کند.

شکل ۱۸: آنالیز زمانی نوسانساز حلقوی تفاضلی سهطبقه مبتنی بر ماسفت با تغییر ولتاژ کنترلی در بازه ۶/۶ تا ۰/۹ ولت Figure 18. Transient analysis of MOSFET-based three-stage DRO with control voltage change in the range of 0.6 to 0.9 V

شکل ۱۹: تأثیر تغییرات ولتاژ کنترلی Vctrl در نوسانساز حلقوی تفاضلی مبتنی بر ماسفت بر روی (الف) فرکانس نوسان، (ب) توان مصرفی Figure 19. The effect of changes in control voltage Vctrl in MOSFET-based DRO on (a) oscillation frequency, (b) power consumption

در شکل ۲۰ تأثیر تغییرات ابعاد ترانزیستور و تغییر ولتاژ کنترل Vctrl بر روی مقدار PDP نوسان ساز پیشنهادی مبتنی بر ماسفت نشان داده شده است. با توجه به شکل ۲۰(الف) مشخص است که با افزایش ابعاد ترانزیستور وضعیت معیار PDP بدتر می شود و همچنین در مقایسه با نمونه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی معیار PDP آن بدتر است. همچنین با توجه به شکل ۲۰(ب) مقدار PDP برای ولتاژ کنترل ۶/۶ ولت کمترین مقدار است؛ اما همچنان مقدار PDP نسبت به نمونه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی بدتر است.

در ادامه تأثیر تغییرات دما بر روی عملکرد نوسانساز سهطبقه تفاضلی مبتنی بر ماسفت موردبررسی قرار گرفته است. در شکل ۲۱ تأثیر تغییرات دما بر روی PDP نوسانساز پیشنهادی مبتنی بر ماسفت با در نظر گرفتن ابعاد مختلف (افزایش ۱ تا ۵ برابری ابعاد ترانزیستورهای سلول تأخیر) و ولتاژهای تغذیه مختلف (۸/۰ ولت تا ۱ ولت با گامهای ۰/۱ ولت) نشان داده شده است. نتایج بیانگر آن است که PDP نسبت به تغییرات دما مقاوم است اما نسبت به نمونه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی مقدار آن بالاتر است.

شكل ۲۰: تغييرات PDP نوسانساز حلقوى تفاضلى مبتنى بر ماسفت برحسب (الف) تغيير عرض ترانزيستور، (ب) ولتاژ كنترل Figure 20: PDP changes of MOSFET-based DRO in terms of (a) transistor width change, (b) control voltage

شکل ۲۱: تأثیر تغییرات دما بر روی PDP نوسانساز حلقوی تفاضلی مبتنی بر ماسفت (الف) با تغییر عرض ترانزیستورها، (ب) با تغییر ولتاژ تغذیه Figure 21: The effect of temperature changes on the PDP of the MOSFET-based DRO (a) by changing the width of the transistors, (b) by changing the supply voltage

در شکل ۲۲ تأثیر تغییرات ولتاژ تغذیه بر روی PDP نوسانساز پیشنهادی مبتنی بر ماسفت نشان داده شده است. با توجه به شکل ۲۲ با تغییر ولتاژ تغذیه در بازه ۸/۰ ولت تا ۱ ولت مقدار PDP از ۲۴/۲ فمتو ژول تا ۱۹/۸ فمتو ژول تغییر می کند. تغییر ۲۵ درصدی در ولتاژ تغذیه به تغییر ۲۲ درصدی در مقدار PDP می شود و محدوده تغییرات PDP پایین است؛ اما در مقایسه با نمونه مبتنی بر ترانزیستور اثر میدان نانولوله کربنی مقدار PDP بالا است.

شکل ۲۲: تأثیر تغییرات ولتاژ تغذیه بر روی PDP نوسانساز حلقوی تفاضلی مبتنی بر ماسفت Figure 22: Effect of supply voltage changes on PDP of MOSFET-based DRO

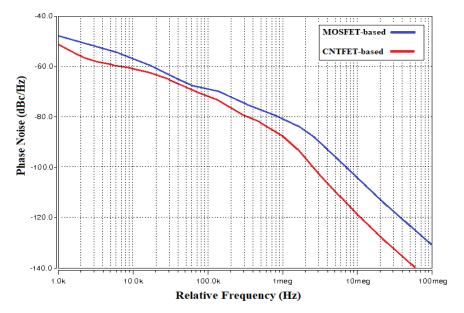

در شکل ۲۳ نویز فاز نوسانساز پیشنهادی مبتنی بر CNTFET با نمونه پیادهسازی شده با ماسفت جهت مقایسه نشان داده شده است. با توجه به شکل ۲۰، نویز فاز نوسانساز پیشنهادی مبتنی بر CNTFET در آفستهای ۱ مگاهرتز و ۱۰ مگاهرتز به ترتیبdBc/Hz و 118.75 dBc/Hz- است. همچنین، نویز فاز نوسانساز پیشنهادی مبتنی بر ماسفت در آفستهای ۱ مگاهرتز و ۱۰ مگاهرتز به ترتیب 81.25 dbc/Hz- و 21.25 است. با بررسی نتایج نویز فاز نیز مشاهده می کنیم که طرح پیشنهادی مبتنی بر CNTFET عملکرد بهتری نسبت به نمونه ماسفت از خود نشان می دهد.

شکل ۲۳: نویز فاز نوسان ساز حلقوی تفاضلی پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی و مقایسه آن با نمونه مبتنی بر ماسفت Figure 23: Phase noise of the proposed DRO based on CNTFET and its comparison with the MOSFET-based implementation

برای مقایسه بهتر با سایر کارها معیار شایستگی دیگری بر اساس تأثیرگذاری نویز فاز بهصورت رابطه (۷) در نظر گرفته میشود. این معیار شایستگی در جدول ۳ با عنوان معیار شایستگی نویز مشخص شده است.

$$FoM_{Ph.} = L(\Delta f_{offset}) - 20\log(\frac{f_0}{\Delta f_{offset}}) + 10\log(P_{DC})$$

(Y)

که در اینجا  $\Delta f_{offset}$  نویز فاز اندازه گیری شده در فرکانس افست  $\Delta f_{offset}$ ،  $f_0$  فرکانس نوسان و  $P_{DC}$  توان مصرفی برحسب میلی وات است.

| معيار شايستگ         | معیار شایستگی          | نویز فاز در            | توان مصرفی          | فركانس نوسان                  | تغذيه        | فناورى                    | اختار  |

|----------------------|------------------------|------------------------|---------------------|-------------------------------|--------------|---------------------------|--------|

| نويز فاز<br>(dBc/Hz) | PDP                    | ا مگاهر تز<br>(dBc/Hz) | (ميکرو وات)         | (گیگاهر تز)                   | (ولت)        | 0,,,                      | 5      |

|                      | (فمتو ژول)             |                        |                     |                               |              |                           |        |

| -                    | •/• 187                | -                      | ۲۵/۵۰۲              | 11./91                        |              | 22                        | [١۵]   |

| -                    | •/• ٢٢٢                | -                      | 84/147              | YY/81                         | • /Y         | 32 nm<br>DG-CNTFET        | [14]   |

| -                    | •/• 189-•/• 184        | -                      | ۲۵/۵۱-۲۸/۴۹         | ۱ <i>۰۷/۶</i> –۱۱ <i>۰</i> /۹ |              |                           |        |

| -                    | •/•٧۴٨                 | -                      | $\chi/\chi\chi\chi$ | ৪/۳۹                          |              | 32nm<br>CMOS-<br>CNTFET   |        |

| -                    | •/•۴١٢                 | -                      | ۴/۹۷۳               | ۲۰/۰۹۳                        | • / <b>A</b> |                           |        |

| -                    | •/• ٢٩٢                | -                      | ٣/٩١٧               | 22/22                         |              |                           |        |

| -                    | ٠/٠٨١٣                 | -                      | ۲/۸۵۹               | ۵/۸۵                          |              |                           |        |

| -                    | ١/٤٢۵-١/٨١۶            | -                      | ۵/۳۱-۲۰/۱۸          | ۰/۶۲-۱/۸۵                     | • / A        | 32 nm<br>CMOS-<br>CNTFET  | [١٣]   |

| -                    | 1/TQ&-1/V99            | -                      | ۳/۲۲-۱۳/۶۵          | •/47-1/78                     |              |                           |        |

| -                    | ۸/•۳-۸/۹۴              | -                      | 22/7° • -77/27      | •/۴١-•/۶۶                     | • / ٨        | 180 nm                    | [۲۰    |

| -                    | •/•۵۵۸-•/۵YA           | -                      | 97/49-120/98        | 274/08-24/29                  |              | CMOS                      |        |

| -                    | ·/· XYY-·/ 170         | -                      | <b>٨۶/٨٣-١٩٩/١٧</b> | 98/11-198/14                  | • / ٨        | 32 nm<br>CNTFET           | [\Y    |

| -                    | •/١٢٨-•/١٨١            | -                      | ۱۳۹/۹۹-۲۹۴/۵۸       | ۵۵/۰۴-۱۴۰/۸۶                  |              |                           |        |

| -                    | •/•••••••••            | -                      | ٣/١١-٣/۴۶           | 198/00-856/88                 |              |                           |        |

| -                    | •/••٢١-•/••٣۶          | -                      | ۳/۷۵-۴/۵۵           | 178/71-11.1/18                | •/٨          | 16 nm<br>GNRFET           | [18]   |

| -                    | •/••٢٣-•/••۴۴          | -                      | ۴/۲۳-۵/۸۶           | 9F/V+-189/81                  |              |                           |        |

| -                    | •/•&٣-•/•9٣            | -                      | ۱۴/۰۲-۱۸/۷۸         | WW/8F-FW/VF                   |              |                           |        |

| -                    | ۰/۰۵۹-۰/۱۸۰            | -                      | 10/44-11/08         | ۱۶/۶۹-۴۰/ <i>۸۶</i>           |              |                           | Ē s a  |

| -                    | ۰/۰۵۸-۰/۱۴۱            | -                      | 10/37-29/18         | ۲۰/۵۴-۲۶/۱۱                   | . / A        | 32 nm<br>CNTFET           | [17]   |

| -                    | •/•۶۴۵-•/٣•٩           | -                      | <i>۱۶/۹</i> ۸-۲۹/۵۵ | ٩/۵۶-۲۵/۳۷                    | • / <b>A</b> |                           |        |

| -                    | •/•۶۲-•/۲•             | -                      | <b>۱۶/۶۳-۴۳/۸۰</b>  | 10/81-19/10                   |              |                           |        |

| -                    | •/•۶٩٢-•/۴۹۵           | -                      | 18/48-48/4.         | ۶/۹۸-۱۸/۵۹                    |              |                           |        |

| _                    | ۰/• ۹۳۹-۱/• ۹ <b>۸</b> | -                      | ·/\\\-\/٣٣          | ۱۹/V۵-۱VX/V1                  | •/٨          | 16 nm                     | [19    |

| - 103/11             | _                      | - ۹۸                   | 18                  | ۰/۲۶۱–۱/۳۲                    | ۱/٨          | GNRFET<br>180 nm<br>CMOS  | [٣٣    |

| - 181/8.             | -                      | - 118                  | ۶۰۱۰                | ۳/۱–۱۰                        | ۱/٨          | 180 nm<br>CMOS            | [74    |

| - 10V/T·             | -                      | - 84                   | ۷۸۵                 | ۰/۰۰۱–۱۳/۸                    | ١/٢          | 65 nm<br>CMOS             | [۲۵    |

| - 181/46             | -                      | - 1.4/1                | ۹۹۸۰                | 24/12                         | ١            | 180 nm<br>GFET            | [79    |

| -                    | _                      | -                      | 820                 | ٣/١٢-۵/٢۶                     | ۱/۸          | 180 nm<br>CMOS-<br>CNTFET | [77]   |

| - 2.2/12             | ۶۲/۲ <b>۰</b> ۸-۵/۳۳   | - 17٣                  | ۷۵۰۰                | ۶-۲۰                          | ١            | 32 nm                     | ۲۸]    |

| - 101/48             | _                      | - 118                  | ۶                   | •/۴۶•                         | ۱/۵          | CNTFET<br>CNTFET          | [٢٩    |

| - 7/۶٨               | •/•=•188/•49           | – λλ                   | ۵/۱۷-۳۲/۶۸          | ۴۵/۷۰-۱۱۰/۱۸                  | •/٩          | 32 nm                     | بنهادی |

عملکرد نوساز ساز تفاضلی پیشنهادی مبتنی بر ترانزیستور اثر میدان نانولوله کربنی با سایر کارهای دیگر مرتبط با طرحهای توان پایین پیشنهادشده در مقالات در جدول ۳ مقایسه شدهاند. همان طور که مشاهده می شود، تحقیق فعلی عملکرد بهبودیافته در مقایسه با تحقیقهای جدید و بهروز از خود نشان داده و به کمترین PDP با ولتاژ تغذیه ۰/۹ ولت منجر شده است. در عین حال فرکانس نوسان بالایی ارائه کرده و محدوده وسیعی از تنظیم را دارا است. شایان ذکر است که طرح پیشنهادی تنها نمونه با خروجی تفاضلی است و سایر کارهای پیشین مقایسه شده همگی بهصورت تکسر هستند. از لحاظ معیار شایستگی نویز فاز تنها طرح ارائه شده در مرجع [۲۹] نسبت به طرح پیشنهادی در این پژوهش خیلی جزئی برتری دارد. از لحاظ معیار شایستگی PDP وقتی طرح گزارششده در مرجع [۲۹] را مورد ارزیابی قرار میدهیم متوجه می شویم که این ساختار با این که یک ساختار سهطبقه است اما از لحاظ مقدار شایستگی PDP بسیار بالا بوده و توان مصرفی بالایی دارد. فلذا، طرح پیشنهادی در این پژوهش نسبت به طرح مذکور در مرجع [۲۹] قابلیتهای بسیار بالایی دارد.

## ۴- نتیجهگیری

در این پژوهش، طراحی و شبیهسازی یک نوسانساز حلقوی سهطبقه تفاضلی با عملکرد بالا بر اساس ترانزیستور اثر میدان نانولوله کربنی ارائه شد که میتواند فرکانس نوسان آن با ولتاژ تغذیه ۹/۹ ولت در بازه ۱۱۰ گیگاهرتز تا ۱۲۰ گیگاهرتز با تغییر تعداد نانولولهها تغییر کند و در عین حال توان مصرفی آن در بازه ۳۳/۳ میکرو وات تا ۱۶۲ میکرو وات باشد. همچنین با تغییر ولتاژ کنترل موجود در ساختار سلول تأخیر پیشنهادی میتوان فرکانس نوسان نوسانساز تفاضلی پیشنهادی را در بازه بسیار وسیعی از ۴۵/۲ گیگاهرتز تا ۱۱۰/۱۸ گیگاهرتز تغییر داد و در عین حال توان مصرفی آن در بازه ۳۳/۶۸ میکرو وات باشد. نوسانساز حلقوی طراحی شده میتوان فرکانس نوسان ناولوله کربنی ویژگیهای امیدوارکننده ای نسبت به نمونه مبتنی بر ماسفت و همچنین نسبت به سایر نوسانسازهای موجود عملکرد فوق العاده خوبی از خود نشان داد.

**سپاسگزاری** با تشکر از استاد محترم جناب آقای مهندس امیر باغی رهین، که با راهنماییهای دلسوزانه ایشان این کار پژوهشی به سرانجام رسید.

#### مراجع

- [1] A. Moghateli,H. Momenzadeh and M. Nader Kakai, "Simulation and investigation of parameters affecting the reduction of power consumption in multiplication circuits using CNT transistor technology," *Journal of Southern Communication Engineering*, vol. 10, no. 38, pp. 39-50, 2020 [in persian].

- [2] A. Baghi Rahin and V. Baghi Rahin, "A new 2-input CNTFET-based XOR cell with ultra-low leakage power for low-voltage and low-power full adders," *Journal of Intelligent Procedures in Electrical Technology (JIPET)*, vol. 10, no. 37, pp. 2322-3871, 2019 [in persian].

- [3] A. Baghi Rahin, A. Kadivarian and V. Baghi Rahin, "Design of a Full Swing 20-Transistors Full Adder Cell based on CNTFET with High Speed and Low PDP," *International Conference on Electrical Engineering (ICEE)*, 2022, pp.546-550, doi: 10.1109/ICEE55646.2022.9827050.

- [4] B.Q. Wei, R. Vajtai and P.M. Ajayan, "Reliability and Current Carrying Capability of Carbon Nanotubes," *Appl. Phys. Lett.*, vol. 79, pp. 1172-1174, 2001, doi: 10.1063/1.1396632.

- [5] J. Deng and H.S. P. Wong "A compact SPICE model for carbon nanotube field effect transistors including non-idealities and its application Part II: Full device model and circuit performance benchmarking", *IEEE Trans Electron Devices*, vol. 54, no. 12, pp. 3195-3205, Dec 2007, doi: 10.1109/TED.2007.909043.

- [6] N. Cheraghi Shirazi, E. Abiri Jahromi and R. Hamzehyan, "Investigating the performance of active vector and inductor capacitors in the resonant circuit of integrated VCOs with 0.18 μm CMOS technology," *Journal of Southern Communication Engineering*, vol. 7, no. 26, 2017 [in persian].

- [7] N. Cheraghi Shirazi and R. Hamzehyan,, "Evaluation of phase noise performance of voltage-controlled integrated inductors and active inductors with 0.18 μm CMOS technology," *Journal of Southern Communication Engineering*, vol. 7, no. 25, 2018 [in persian].

- [8] Y. Toh and J. A. McNeill, "Single-ended to differential converter for multiple-stage single-ended ring oscillators," *IEEE J. Solid-State Circuits*, vol. 38, no. 1, pp. 141–145, 2003, doi: 10.1109/JSSC.2002.806262.

- [9] B. Razavi, "Design of monolithic phase locked loops and clock recovery circuits: A tutorial," in *Monolithic Phase-Locked Loops and Clock Recovery Circuits: Theory and Design*, IEEE, 1996, pp.1-39, doi: 10.1109/9780470545331.ch1.

- [10] J. Savoj and B. Razavi, "A 10-Gb/s CMOS clock and data recovery circuit with a half-rate linear phase detector," *IEEE J. Solid-State Circuits*, vol. 36, no. 5, pp. 761–768, 2001, doi: 10.1109/4.918913.

- [11] B. Fahs, W. Y. A. Ahmad and P. Gamand, "A two-stage ring oscillator in 0.13 μm CMOS for UWB impulse radio," *IEEE Trans. Microwave Theory Tech.*, vol. 57, no. 5, pp. 1074–1082, 2009, doi: 10.1109/TMTT.2009.2017246.

- [12] H. Thabet, S. Meillere, M. Masmoudi, J. Seguin, H. Barthelemy and K. Aguir, "A low power consumption CMOS differential-ringVCO for a wireless sensor," in *Proc. 9th IEEE Int. New Circuits Systems Conf.*, 2011, pp. 81–84, doi: 10.1109/NEWCAS.2011.5981224.

- [13] D. Fathi and B. Mohammadi, "Millimeter Wave Ring Oscillator Using Carbon Nano-Tube Field Effect Transistor in 150 GHz and Beyond," *Circuits and Systems*, vol. 4, no. 2, pp. 157-164, 2013, . doi: 10.4236/cs.2013.42021.

- [14] A. Baghi Rahin, A. Kadivarian, S. Naseri Akber and V. Baghi Rahin, "Tunable Ring Oscillators Based on Hybrid FGMOS/CNTFET Inverters with High Frequency and Low Power," *International Conference on New Researches and Technologies in Electrical Engineering (ICNRTEE)*, University of Science and Culture (USC), Tehran, Iran, 2023.

- [15] A. Baghi Rahin, A. Kadivarian and V. Baghi Rahin, "Investigation of Different Combinations of CNTFET and MOSFET in the Structure of a Hybrid Ring Oscillator," *IEEE 6th Conference on Technology in Electrical and Computer Engineering (ETECH 2021)*, Tafresh University, Tafresh, Iran ,2021.

- [16] A. Baghi Rahin, A. Kadivarian and V. Baghi Rahin, "Extremely High Frequency and Low Power Ring Oscillators Using DG-CNTFET Transistors," *IEEE 6th Conference on Technology in Electrical and Computer Engineering (ETECH 2021)*, ), Tafresh University, Tafresh, Iran , 2021.

- [17] A. Baghi Rahin, A. Kadivarian, S. Naseri Akbar and V. Baghi Rahin, "Tunable Millimeter Wave Ring Oscillator Using GNRFET," *The 7th National Conference of Applied Researches in Electrical, Mechanical and Mechatronics Engineering*, Tehran, Iran, 2023.

- [18] A. Baghi Rahin, A. Kadivarian, S. Naseri Akbar and V. Baghi Rahin, "Extremely High Frequency Voltage Controlled Ring-Oscillator Based-on NAND Gate Using CNTFET," *The 7th National Conference of Applied Researches in Electrical, Mechanical and Mechatronics Engineering*, Tehran, Iran, 2023.

- [19] A. Baghi Rahin, A. Kadivarian and M. Dadgar, "Ring Oscillator with Frequency Adjustment and Reconfiguration Capability Using Switched NAND-NOR," 12<sup>th</sup> Majlesi Conference on Electrical Engineering, Isfahan, Iran, 2023.

- [20] A. Baghi Rahin, A. Kadivarian and M. Dadgar, "GNRFET-based Voltage Controlled Ring Oscillator Using GDI NAND Gate," *12<sup>th</sup> Majlesi Conference on Electrical Engineering*, Isfahan, Iran, 2023.

- [21] A. Baghi Rahin, M.H. Akhtarzadeh, A.S. Alijanpour and V. Baghi Rahin, "Tunable Ring Oscillator Based on DTMOS and FGMOS Inverters with High Frequency and Low Power in 180 nm CMOS Technology," 8th National Conference on Modern Studies and Resech in Computer, Electrical, and Mechanical Sciences of Iran, Tehran, Iran, 2022.

- [22] J. Jalil, M. B. I. Reaz and M. A. M. Ali, "CMOS Differential Ring Oscillators: Review of the Performance of CMOS ROs in Communication Systems," in *IEEE Microwave Magazine*, vol. 14, no. 5, pp. 97-109,

July-Aug. 2013, doi: 10.1109/MMM.2013.2259401.

- [23] Y. Sun and M. Jiang, "A low power, and wide tuning range ring voltage controlled oscillator," *IEEE International Conference on Consumer Electronics-Asia (ICCE-Asia)*, Seoul, Korea (South), 2016, pp. 1-4. doi: 10.1109/ICCE-Asia.2016.7804742.

- [24] S. Kamran and N. Ghaderi, "A novel high speed CMOS pseudo-differential ring VCO with wide tuning control voltage range," *Iranian Conference on Electrical Engineering (ICEE)*, Tehran, Iran, 2017, pp. 201-204. doi: 10.1109/IranianCEE.2017.7985438.

- [25] S. Askari and M. Saneei, "Design and analysis of differential ring voltage controlled oscillator for wide tuning range and low power applications," *Int. J. Circuit Theory Appl.*, vol. 47, no. 2, pp. 204-216, Feb. 2019, doi: 10.1002/cta.2582.

- [26] A. Safari and M. Dousti, "Ring oscillators based on monolayer Graphene FET," *Analog Integrated Circuits and Signal Processing*, vol. 102, pp. 637–644, 2020, doi: 10.1007/s10470-020-01624-x.

- [27] S. Rahane and A. Kureshi, "A low power and linear voltage controlled oscillator using hybrid CMOS-CNFET technology," *International Journal of Applied Engineering Research*, vol. 12, no. 9, pp. 1969– 1973, 2017.

- [28] H. Sarbazi, R. Sabbaghi-Nadooshan and A. Hassanzadeh, "A CNT based VCO with extremely low phase noise and wide frequency range for PLL application," *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, vol. 34, no. 5, 2021, doi:10.1002/jnm.2891.

- [29] A. Taghavi, C. Carta, T. Meister, F. Ellinger, M. Claus and M. Schroter, "A CNTFET Oscillator at 461 MHz," *IEEE Microwave and Wireless Components Let-ters*, vol. 27, no. 6, 2017, doi:10.1109/LMWC.2017.2701312.

#### **COPYRIGHTS**

©2025 by the authors. Published by the Islamic Azad University Bushehr Branch. This article is an openaccess article distributed under the terms and conditions of the Creative Commons Attribution 4.0 International (CC BY 4.0) <u>https://creativecommons.org/licenses/by/4.0</u>