https://doi.org/10.30495/jce.2022.691133

# Vol. 11/ No. 44/Summer 2022

**Research Article**

# Design of Low-Area, Low-Power and High-Speed Comparator in 65 nm

# **FinFET Technology**

Navid Sabzevari, MSc <sup>1,4</sup> <sup>[D]</sup> Mohammad Reza Yousefi, Assistant Professor <sup>2,4</sup> <sup>[D]</sup> | S. Mohammadali Zanjani, Assistant Professor <sup>3,4</sup> <sup>[D]</sup>

<sup>1</sup>Department of Electrical Engineering, Najafabad Branch, Islamic Azad University, Najafabad, Iran, Navid.sabzevari@gmail.com

<sup>2</sup>Department of Electrical Engineering, Najafabad Branch, Islamic Azad University, Najafabad, Iran, mr-yousefi@iaun.ac.ir

<sup>3</sup>Department of Electrical Engineering, Najafabad Branch, Islamic Azad University, Najafabad, Iran, sma\_zanjani@pel.iaun.ac.ir

<sup>4</sup>Smart Microgrid Research Center, Najafabad Branch, Islamic Azad University, Najafabad, Iran.

#### Correspondence

S. Mohammadali Zanjani, Assistant Professor, Department of Electrical Engineering, Najafabad Branch, Islamic Azad University, Najafabad, Iran, sma\_zanjani@pel.iaun.ac.ir

Received: 15 March 2022 Revised: 18 April 2022 Accepted: 12 May 2022

#### Abstract

In the present study, a new low-power and high-speed comparator circuit is designed in 65 nm fin field-effect transistor (FinFET) technology. Moreover, by properly using the capabilities of FinFET technology, the number of transistors is reduced, and subsequently, a smaller area is occupied. Replacing MOSFET transistors with FinFETs reduces the delay and power consumption of the circuit, so the overall performance is improved. The first innovation of the proposed design is that to reduce the size and power consumption, two transistors were removed and the back gates of two transistors were cross-coupled. The second innovation is the connection of back gates to other suitable points of the circuit that increase the speed of comparison. In this study, a supply voltage of 0.8 V is applied to the circuit to show that the proposed modifications with FinFET reduce the delay to 272 ps and power consumption to  $6.7 \,\mu$ W.

Keywords: Comparator, FinFET, High-speed, Low-area, Low-power

## Highlights

- New low-power and high-speed comparator circuit designed in 65 nm fin field-effect transistor (FinFET).

- Reduction of the number of transistors and subsequently, smaller area.

- Reduction of the delay and power consumption of the circuit by replacing MOSFETs with FinFETs.

**Citation:** N. Sabzevari, M. R. Yousefi, and S. M. Zanjani, "Design of a Low-Area, Low-Power and High-Speed Comparator in 65 nm FinFET Technology," *Journal of Southern Communication Engineering*, vol. 11, no. 44, pp. 9–18, 2022, doi: 10.30495/jce.2022.691133.

# **1- INTRODUCTION**

The increasing need for low-power, high-speed and minimum area circuits such as analog-to-digital (A/D) in today's technology makes it easier to move towards dynamic comparator designs with maximum speed and low power consumption [1,2]. One of the most important blocks in ADCs is the comparator whose speed and power consumption are very influential in these circuits [3,4,5].

A fin field-effect transistor (FinFET) is a multi-gate device, a MOSFET built on a substrate where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double or even multi gate structure [6,7]. The FinFET devices have significantly faster switching times and higher current density than planar CMOS technology [8,9].

So far, fin field-effect transistor (FinFET) technology has been used in various researches [10,11].

A p-type Inverted-T FinFET has been optimally structured in [12], in which, FinFET has a higher layout efficiency and can thus provide larger drain current under the same dimension as that of a SOI FinFET by securing the extended channels of ultrathin body on the field region.

A FinFET transistor-based domino technique DNDFTDL is designed for low-power, high-speed and improved noise performance in [13], which the concept of current division is explored below the evaluation network for enhancement of performance parameters and simulations are carried out for 32-nm complementary CMOS and FinFET node using HSPICE for 2-, 4-, 8- and 16-input OR gates with a DC supply voltage of 0.9V.

Therefore, in this paper, after studying a few conventional circuits, a new high-speed and low-power comparator is designed and simulated in 65 nm FinFET technology. A comparison between the proposed comparator and previous works indicates the acceptability of the design.

In the second section, conventional comparators are mentioned. The third section, describes the fin field-effect transistor technology. In the fourth section, the results and their discussion are stated and in the last section, the conclusion is given.

### 2- CONVENTIONAL COMPARATORS

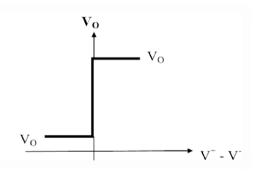

The output of an ideal comparator is shown in Figure 1. The output is "0" if the input signal is less than the reference voltage and is "1" if the input is greater than the reference voltage.

Figure 1. Output of an ideal comparator

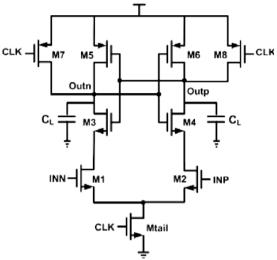

Figure 2 shows a conventional comparator circuit that was proposed in [14]. In this figure, M1 and M2 are the input transistors and their source can be connected to GND through Mtail whenever CLK is ON, so the dynamic circuit performs the comparison. If INN<INP, then M2 turns on and M1 turns off. In this case, the current flow through M2, M4, and M6 increases and vice versa.

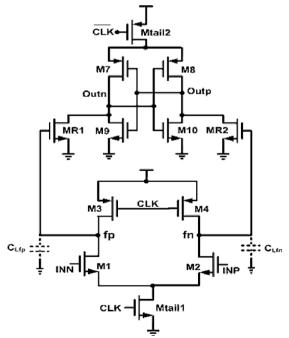

The circuit shown in Figure 3, is the next generation of the circuit shown in Figure 2. If INN<INP, then the drain current of M2 is more than that of M1, and the voltage of fn drops to zero. Moreover, since MR2 goes to zero, while MR1 is turned on and goes to one; the voltage of OUTN and OUTP go to zero and one. Consequently, M8 is turned on and connects OUTP to VDD, while OUTN is connected to GND through the M9.

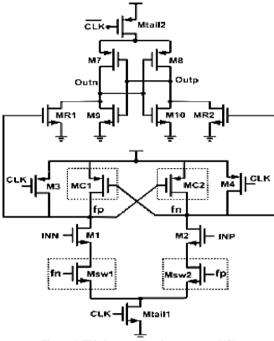

As shown in Figure 4, MC1 and MC2 are respectively, in parallel with M3 and M4, and cross-coupled. This can help the voltage of fp to reach VDD faster, and similarly, the voltage of fn to GND. Since M1 is connected to fp, it prevents fp from going to VDD; the source of M1 is connected to GND through Mtail, which leads to a delay. Therefore, MSW1 is added to the circuit to disconnect M1 from GND while fp increases. Similarly, MSW2 is added to disconnect M2 from GND while fn increases to VDD [10]. In table 1, the results of conventional comparator circuits are shown.

| TABLE 1. Result of the conventional comparators |                                      |                                     |                                                               |

|-------------------------------------------------|--------------------------------------|-------------------------------------|---------------------------------------------------------------|

| Structure                                       | Conventional Dynamic<br>Comparator 1 | Double-tail Dynamic<br>Comparator 2 | Double-tail Dynamic<br>Comparator 3                           |

| Technology CMOS                                 | 180 nm                               | 180 nm                              | 180 nm                                                        |

| Supply voltage (V)                              | 0.8                                  | 0.8                                 | 0.8                                                           |

| Delay/Log vin (pS/dec.)                         | 940                                  | 358                                 | 294                                                           |

| Energy per conversion (pJ)                      | 0.3                                  | 0.27                                | 0.24<br>(Without M <sub>sw1</sub> & M <sub>sw2</sub> : 0.256) |

| Estimated area (µm <sup>2</sup> )               | 16*16                                | 28*12                               | 28*14                                                         |

Figure 2. First conventional comparator [10]

Figure 3. Second conventional comparator [10]

Figure 4. Third conventional comparator [10]

### **3- FIN FIELD-EFFECT TRANSISTOR**

FinFETs are a very promising alternative to bulk MOS transistors in the nanoscale [15]. A FinFET has two gates that make it more efficient. This can reduce leakage current and short channel effect [16,17]. The main goal in very large-scale integration (VLSI) designs is to achieve the best possible efficiency with low power consumption [18,19]. This goal can easily be achieved by substituting FinFET circuits for CMOS blocks such as 6T-SRAM [20,21], 8T-SRAM [22,23] and 9-T SRAM [24,25]. Analysis of performance metric, process variation, and temperature effect Nanoscale FinFET based SRAM cell design is described in [26] and [27].

Despite the raw material limitations in the fabrication of transistors, the speed of progress in designing and CMOS technology scaling is very slow and the size reduction is very limited. One of our challenges is to reduce the leakage current which includes sub-threshold leakage and gate leakage [28,29].

Besides utilizing area more efficiently, FinFETs are also very efficient in controlling leakage currents, compared to CMOS transistors [30,31]. Better control on the channel is achieved since the channel is surrounded by the gate and there is an improvement in the channel effects. Moreover, the higher mobility of carriers reduces the sub-threshold leakage current [32].

## 4- PROPOSED CIRCUIT

Most of the circuits designed in FinFET technology are digital and a small percentage of them are analog. In this study, an analog comparator circuit is designed and presented. To compare the proposed circuit in FinFET technology with the conventional CMOS circuits, a FinFET circuit was required. However, there was no available FinFET analog circuit. Indeed, very little work has been done on using FinFET in the ana-log domain as it is an innovative and still developing area. Therefore, for a better comparison of the proposed comparator circuit in 65 nm FinFET technology with conventional designs, a prior art design is required. It was decided to redesign an existing 180 nm CMOS circuit in 65 nm FinFET technology for a comparison with previous designs.

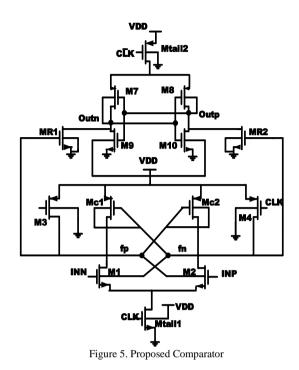

In the proposed circuit (Figure 5) several transistors are eliminated, so the delay, power consumption, and the occupied area are reduced. To reduce the size and power consumption, transistors MSW1 and MSW2 are replaced by the M1 and M2as back gates.

Mc1 and Mc2 are used to cross-coupled connected to fn and fp points. The two transistors MR1 and MR2 are connected to the points fn and fp, so they work with the rapid changes of fn and fp, and with rapid shutdown, help reduce power consumption. Therefore, the back gates of these two transistors are also connected to GND to be in their weakest state and turn off faster when fn or fp goes to zero.

As the voltage of fn drops, M1 would go off. Moreover, the back gate of M2 is connected to fp, and the decrease in the voltage of fp results in disconnection from GND. Therefore, by using proper back gates, two fewer transistors are needed, meanwhile, power consumption and chip area are reduced. Additionally, the overall switching speed increases because parasitic elements are reduced.

In conventional comparator circuits, speed increases with the proper use of positive feedback. Thus, in the proposed circuit, back gates and cross-coupled positive feedback are properly combined to reduce the overall delay significantly. Higher speed and lower power dissipation are achieved by connecting the gate of MC1 to fn, the gate of MC2 to fp, the gate of M7 to the drain of M8, and the gate of M8 to the drain of M7. The back gates of MR1 and MR2 are connected to GND to put them in their weakest state to increase the switching speed. It is worth mentioning that the back gate of N-channel transistors should be connected to VDD and P channel transistors' back gates of M10 and M9 are connected to VDD to turn off the MR1 and MR2 later and are located in the upper cross-couple.

The two transistors MR1 and MR2 are connected to the points fn and fp, so they work with the rapid changes of fn and fp, and with a rapid shutdown, help reduce power consumption. Therefore, the back gates of these two transistors are also connected to GND to be in their weakest state and turn off faster when fn or fp goes to zero.

M3 and M4 are P-type and their back gates are connected to GND. Mtail1 is located at the bottom of the circuit and its back gate is connected to VDD. This transistor has a profound impact on the speed of the proposed circuit. Similarly, Mtail2 is a P-type transistor located at the top of the circuit with its back gate connected to GND. Since N-channel transistors are stronger, they can pass more current and are faster than the P-channel transistors.

In other words, the innovation of the proposed design is that to reduce the size and power consumption, two transistors MSW1 and MSW2 were removed and the back gate of two transistors M1 and M2 were cross-coupled and both were connected to the points fn and fp. In previous designs, the MSW1 transistor was cut off as the fn voltage decreased, but now, as it decreases, the M1 goes off because its back gate is connected to the fn. Also, transistor M2, whose back gate is connected to fp, goes off and prevents connection to GND. With proper use of back gates, two transistors are removed, speed is increased and power consumption is reduced. It should be noted that the connection of back gates to two points fn and fp is an innovation and the output power of the transistor is regulated by the current of these two points to optimize power consumption and increase speed. The back gate is not only for connecting to the vdd and ground to increase or decrease the power of the transistor, and by connecting the back gate to other suitable points of the circuit, this can also be done, and according to the type of design and proper use of the back gate can be Increased speed and reduced power consumption.

#### 5- RESULT AND DISCUSSION

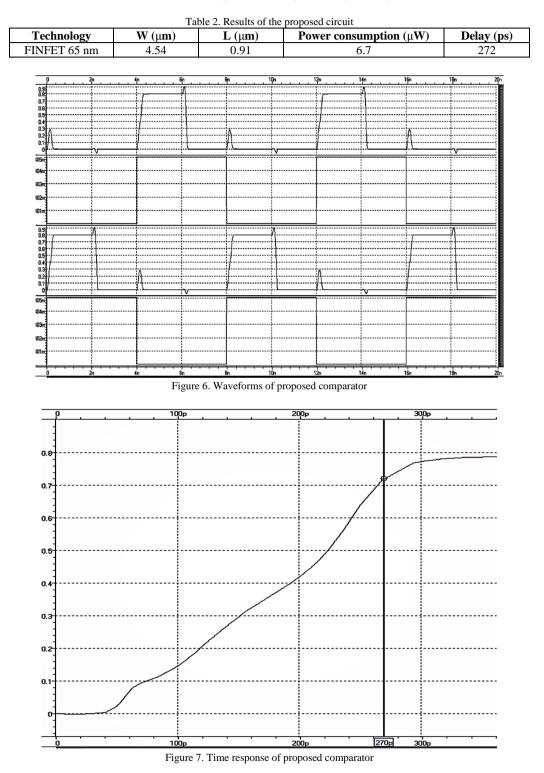

As explained above, the new comparator circuit using the 65 nm FinFET technology, simulated in H-SPICE circuit simulator and the results are shown in Table 2, Figure 6 and Figure 7 respectively.

Proper swing of the outputs indicates the optimal performance of the proposed circuit. The amount of time delay in 90% of the final output level is 272 ps.

Accordingly, the replacement of MOS transistors with FinFETs are more suited to their operating conditions and the overall performance of the circuit is increased significantly.

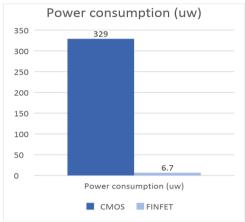

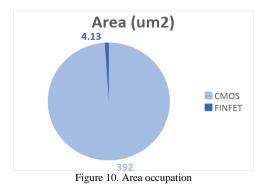

To better compare the results of the proposed circuit with the conventional designs, graphical representations are plotted in Figures 8 to 10.

The difference in the power consumption of the designs with FinFET and CMOS technology is shown in Figure 8. The amount of power consumed in 180 nm CMOS technology is 329  $\mu$ w, while the corresponding value in 65 nm FinFET technology is 6.7  $\mu$ w.

Figure 8. Power consumption of the two designs in FinFET and CMOS technologies

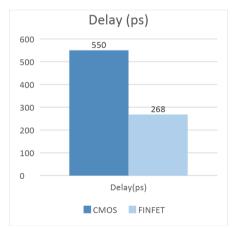

Figure 9 and Figure 10 compare the values of delay and area of the two comparator circuits in different technologies. The delay and occupied area in CMOS technology are 550 pS and 392 um<sup>2</sup>, respectively. These values are reduced to 272 pS and 4.13 um<sup>2</sup> in 65 nm FinFET technology. These results show the superiority of the proposed circuit in FinFET technology.

Figure 9. Delays of two comparator circuits in different technologies

۱۵

#### 6- CONCLUSION

The power consumption of the proposed comparator circuit is 6.7  $\mu$ W, which is 97.96% less than the previous circuit, i.e., the power consumption is reduced about 49 times. The measured delay of the circuit is 272 pS, which decreased by 51.27% compared to the previous circuit. The occupied area of the proposed circuit was 4.13 um<sup>2</sup>, compared to 392 um<sup>2</sup> in the previous circuit, which means a 98.94% decrease. Consequently, all important parameters of the proposed comparator circuit are significantly improved. Using new tools such as CNTFETs and designing in the sub-threshold area are from future works.

#### REFERENCES

- A. Khorami and M. Sharifkhani, "A low-power high-speed comparator for precise applications", *IEEE Trans. on Very Large-Scale Integration (VLSI) Systems*, vol. 26, no. 10, pp. 2038-2049, 2018 ,doi: 10.1109/TVLSI.2018.2833037.

- [2] A. Baghi Rahin, V. Baghi Rahin, "A new 2-input CNTFET-based XOR cell with ultra-low leakage power for low-voltage and low-power full adders", *Journal of Intelligent Procedures in Electrical Technology*, vol. 10, no. 37, pp. 13-22, 2019, dor: 20.1001.1.23223871.1398.10.37.2.6.

- [3] I. Chakraborty, A. Agrawal, K. Roy, "Design of a low-voltage analog-to-digital converter using voltagecontrolled stochastic switching of low barrier nanomagnets", *IEEE Magnetics Letters*, vol. 9, pp. 1-5, May 2018, doi: 10.1109/LMAG.2018.2839097.

- [4] O. Aiello, P. Crovetti, M. Alioto, "Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation", *IEEE Access*, vol. 8, pp. 70890-70899, April 2020, doi: 10.1109/ACCESS.2020.2986949.

- [5] Y. Wang, M. Yao, B. Guo, Z. Wu, W. Fan, J.J. Liou, "A low-power high-speed dynamic comparator with a transconductance-enhanced latching stage", *IEEE Access*, vol. 7, pp. 93396-93403, 2019 ,doi: 10.1109/ACCESS.2019.2927514.

- [6] S.M.A. Zanjani, M. Dousti, M. Dolatshahi, "Inverter-based, low-power and low-voltage, new mixed-mode Gm-C filter in subthreshold CNTFET technology", *IET Circuits, Devices & Systems*, vol. 12, no. 6, pp. 681-688, 2018, doi: 10.1049/iet-cds.2018.5158.

- [7] Y. Cai et al., "Endurance characteristics of negative capacitance FinFETs with negligible hysteresis", *IEEE Electron Device Letters*, vol. 42, no. 2, pp. 260-263, Feb. 2021, doi: 10.1109/LED.2020.3048349.

- [8] V. Varshney, R.K. Nagaria, "Design and analysis of ultra-high-speed low-power double tail dynamic comparator using charge sharing scheme", *International Journal of Electronics and Communications*, vol. 116, Article paper: 153068, 2020 ,doi: 10.1016/j.aeue.2020.153068.

- [9] A. Baghi Rahin, V. Baghi Rahin, "Ultra low voltage and low power 4-2 compressor using FinFET transistors", *Journal of Intelligent Procedures in Electrical Technology*, vol. 9, no. 33, pp. 25-36, June 2018, dor: 20.1001.1.23223871.1397.9.33.3.2.

- [10] Y.J. Chang, K.L. Tsai, Y.C. Cheng, M.R. Lu, "Low-power ternary content-addressable memory design based on a voltage self-controlled fin field-effect transistor segment", *Computers and Electrical Engineering*, vol. 81, no. 106528, Jan, 2020,doi:10.1016/j.compeleceng.2019.106528.

- [11] E. Yu, K. Heo, S. Cho, "Characterization and optimization of inverted-T FinFET under nanoscale dimensions", *IEEE Trans. on Electron Devices*, vol. 65, no. 8, pp. 3521-3527, Aug. 2018 ,doi: 10.1109/TED.2018.2846478.

- [12] S. Garg, T.K. Gupta, "A new technique for designing low-power high-speed domino logic circuits in Fin-FET technology", *Journal of Circuits, Systems and Computers*, vol. 28, no. 10, no. 1950165, 2019 ,doi: 10.1142/S0218126619501652.

- [13] S. Babayan-Mashhadi, R. Lotfi, "Analysis and design of a low-voltage low-power double tail comparator", *IEEE. Trans. on Very Large-Scale Integration (VLSI) system*, vol. 22, no. 2, pp. 343-352, Feb. 2014, doi: 10.1109/TVLSI.2013.2241799.

- [14] G. Leung, S. Wang, A. Pan, P. Gupta and C. O. Chui, "An evaluation framework for nanotransfer printingbased feature-level heterogeneous integration in VLSI circuits", *IEEE Trans. on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 5, pp. 1858-1870, May 2016, doi: 10.1109/TVLSI.2015.2477282.

- [15] R. Kuo, F. Chang, Y. King, C. Lin, "Antifuse OTP Cell in a Cross-Point Array by Advanced CMOS FinFET Process", IEEE Trans. on Electron Devices, vol. 66, no. 4, pp. 1729-1733, 2019.B. Swahn, S. Hassoun, "Gate sizing: FinFETs vs 32nm Bulk MOSFETs", *Proceedings of the IEEE/ACM*, pp. 528–531, 2006, doi: 10.1109/TED.2019.2900282.

- [16] S. Daneshgar et al., "High-power generation for mm-wave 5G power amplifiers in deep sub micrometer planar and FinFET bulk CMOS", *IEEE Trans. on Microwave Theory and Techniques*, vol. 68, no. 6, pp. 2041-2056, 2020, doi: 10.1109/TMTT.2020.2990638.

- [17] N. Agrawal, H. Liu, R. Arghavani, V. Narayanan, S. Datta, "Impact of variation in nano scale silicon and nonsilicon FinFETs and tunnel FETs on device and SRAM performance", *IEEE Trans. on Electron Devices*, vol. 62, no. 6, pp. 1691-1697, 2015, doi: 10.1109/TED.2015.2406333.

- [18] X. Zhang, et. al. "Analysis of 7/8-nm bulk-Si FinFET technologies for 6T-SRAM scaling", IEEE Trans. on Electron devices, vol. 63, no. 4, pp. 1502-1507, 2016, doi: 10.1109/TED.2016.2523885.

- [19] A.G. Akkala, R. Venkatesan, A. Raghunathan, K. Roy, "Asymmetric underlapped sub-10-nm n-FinFETs for high-speed and low-leakage 6T SRAMs", *IEEE Trans. on Electron Devices*, vol.63, no. 3, pp. 1034-1040, 2016, doi: 10.1109/TED.2015.2512227.

- [20] G. Pasandi, S.M. Fakhraie, "An 8T low-voltage and low-leakage half-selection disturb-free SRAM using bulk-CMOS and FinFETs", *IEEE Trans. on Electron Devices*, vol. 61, no. 7, pp. 2357- 2363, 2014, doi: 10.1109/TED.2014.2321295.

- [21] M. Monica, P. Chandramohan, "Characterization of 8T SRAM cells using 16 nm FinFET technology", Proceeding of the IEEE/ICSC, pp. 403-406, Noida, India, Dec. 2016, doi:10.1109/ICSPCom.2016.7980614.

- [22] Y. Yang, J. Park, S.C. Song, J. Wang, G. Yeap, S. Jung, "Single-ended 9T SRAM cell for near-threshold voltage operation with enhanced read performance in 22-nm FinFET technology", *IEEE Trans. on Very Large-Scale Integration (VLSI) Systems*, vol. 23, no. 11, pp. 2748-2752, Nov. 2015, doi: 10.1109/TVLSI.2014.2367234.

- [23] N. Sharma, "Ultra low power dissipation in 9T SRAM design by using FinFET technology", *Proceeding of the IEEE/ICTBIG*, pp. 1-5, Indore, India, Nov. 2016, doi: 10.1109/ICTBIG.2016.7892657.

- [24] A. Guler, N.K. Jha, "Three-dimensional monolithic FinFET-based 8T SRAM cell design for enhanced read time and low leakage", *IEEE Trans. on Very Large Scale Integration (VLSI) Systems*, vol. 27, no. 4, pp. 899-912, April 2019, doi: 10.1109/TVLSI.2018.2883525.

- [25] M.U. Mohammed, M.H. Chowdhury, "Reliability and energy efficiency of the tunneling transistor-based 6T SRAM cell in sub-10 nm domain", *IEEE Trans. on Circuits and Systems II: Express Briefs*, vol. 65, no. 12, pp. 1829-1833, Dec. 2018, doi: 10.1109/TCSII.2018.2874897.

- [26] M. Aghaei Jeshvaghani, M. Dolatshahi, "Design of a low-power universal Gm-C filter in sub-threshold region", *Journal of Intelligent Procedures in Electrical Technology*, vol. 4, no. 15, pp. 3-10, 2013, dor: 20.1001.1.23223871.1392.4.15.1.9.

- [27] S.M.A. Zanjani, M. Dousti, M. Dolatshahi, "A new low-power, universal, multi-mode Gm-C filter in CNTFET technology", *Microelectronics Journal*, vol. 90, pp. 342-352, 2019, doi: 10.1016/j.mejo.2019.01.003.

- [28] S. Chaudhuri, N.K. Jha, "3D vs. 2D analysis of FinFET logic gates under process variations", Proceedings of the IEEE/ICCD, pp. 435–436, 2011, doi: 10.1109/ICCD.2011.6081437.

- [29] M. Xu et al., "Improved short channel effect control in bulk FinFETs with vertical implantation to form selfaligned halo and punch-through stop pocket", *IEEE Electron Device Letters*, vol. 36, no. 7, pp. 648-650, July 2015, doi: 10.1109/LED.2015.2434825.

- [30] B. Raj, A.K. Saxena, S. Dasgupta, "Nanoscale FinFET based SRAM cell design: Analysis of performance metric, process variation, underlapped FinFET, and temperature effect", *IEEE Circuits and Systems Magazine*, vol. 11, no. 3, pp. 38-50, 2011, doi: 10.1109/MCAS.2011.942068.

- [31] R. Chang, C. Lin and M. Ker, "Design of fin-diode-triggered rotated silicon-controlled rectifier for high-speed digital application in 16-nm FinFET process", *IEEE Trans. on Electron Devices*, vol. 67, no. 7, pp. 2725-2731, July 2020, doi: 10.1109/TED.2020.2995145.

- [32] S.M.A. Zanjani, N. Chamanpira, M. Dolatshahi, "Design and simulation of a new sample and hold circuit with a resolution of 12-bit and a sampling rate of 1 GS/s using a dual sampling technique", *Journal of Intelligent Procedures in Electrical Technology*, vol. 9, no. 34, pp. 3-10, 2018, dor: 20.1001.1.23223871.1397.9.34.1.2.